# High Efficiency Offline PWM Controller with Wide VCC Range

# 1. Descriptions

MK2687 is a multi-mode PWM controller optimized for PD/ fast charging applications. Its wide VCC operating voltage range allows it to cover the output range of PD/PPS from 3.3V-23V without using additional windings or linear step-down circuits.

In response to energy efficiency requirements, since PD / fast charging has multiple different output voltages, adaptive multi-mode is adopted. It adjusts to work at DCM /QR/CCM under different loads and different outputs. Under light load, it will work in burst mode to improve efficiency. Its maximum switching frequency is up to 65 kHz.

MK2687 provides comprehensive protection functions, including output overvoltage protection, VCC overvoltage protection, overpower protection, Brown in/out and Secondary side SR short circuit protection, Pin OPEN/SHORT protection.

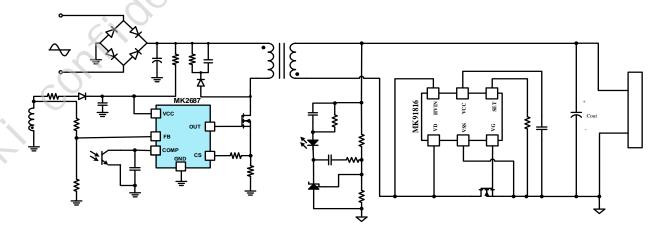

# 3. Typical Application

- AC/DC PD adapter

- AC/DC general power supply

# 2. Features

- Wide range VCC operating voltage (10V-88V)

- Multi-mode control for different output voltages and loads

- Proprietary soft-start circuit reduces SR Vds stress

- Optimized efficiency easily meets energy efficiency labeling

- Over power protection

- Brown in / Brown out Function

- VCC overvoltage protection / Vout overvoltage protection

- Secondary side SR short circuit protection

- External OTP setting protection

- Support PPS wide range output

- SOT23-6 package

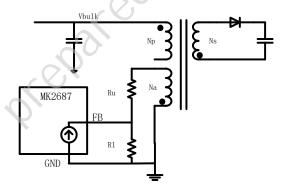

# 4. Simplified Application

Specifications Subject to Change without notice

# 5. Order Information

| Ordering code | Description            |  |

|---------------|------------------------|--|

| MK2687GSA     | SOT23-6, 3000 pcs/reel |  |

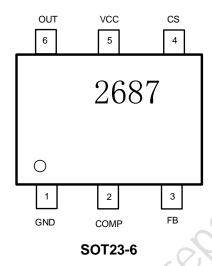

# 6. Pin Package

| VCC 0.3V to +100V                                                   |

|---------------------------------------------------------------------|

| COMP, FB0.3V to +5.5V                                               |

| CS0.7V to + 5.5V                                                    |

| OUT0.3V to +20V                                                     |

| Operating junction temperature40 $^{\circ}$ C to + 155 $^{\circ}$ C |

| 6.2 Recommended | Operations | conditions |

|-----------------|------------|------------|

|-----------------|------------|------------|

| VCC 10                                         | V to 88V      |

|------------------------------------------------|---------------|

| Maximum junction temperature (T <sub>J</sub> ) | +125 °C       |

| 6.3Thermal resistance (2) θ <sub>J</sub>       | <b>. θ</b> ЈС |

| SOT23-6100                                     | 66 °C/W       |

#### Notes:

- (1) Exceeding this range may damage the device

- (2) Measured on JESD51-7, 4 layers PCB

## 7. ESD Performance

|                  |                                                                                                      | Value  | Units |

|------------------|------------------------------------------------------------------------------------------------------|--------|-------|

| ESD parameter    | Human Body Model (HBM), all pins tested in accordance with ANSI/ESDA/JEDEC JS-001 test standards (1) | ± 2000 | V     |

| V <sub>ESD</sub> | Component Charging Model (CDM), according to JEDEC JESD22-C101 standard tests all pins (2)           | ± 1000 | V     |

#### Notes:

- (1) According to the JEDEC JEP155 standard requirements, the Human Body Model (HBM) ESD level required for standard safety production is 500V

- (2) According to the JEDEC JEP157 standard requirements, the component charging model (CDM) ESD level required for standard safety production is 250V

# 8. Electrical Parameters

Unless otherwise specified, T A = 25 °C, VCC=13V.

| parameter                                     | symbol                | conditions                                               | Min  | Тур  | Max  | unit |  |

|-----------------------------------------------|-----------------------|----------------------------------------------------------|------|------|------|------|--|

| Power supply (VCC pin)                        |                       |                                                          |      |      |      |      |  |

| UVLO undervoltage protection turn-on voltage  | Vcc_on                | VCC rises to turn on                                     | 14.5 | 17   | 19.5 | V    |  |

| UVLO undervoltage protection shutdown voltage | Vcc_off               | VCC drops to turn off                                    | 6    | 7.2  | 8.5  | V    |  |

| UVLO undervoltage protection hysteresis (1)   | V <sub>CC_HYST</sub>  |                                                          |      | 10   |      | V    |  |

| VCC startup current                           | ISTARTUP              |                                                          | 2    | 5    | 10   | uA   |  |

| VCC normal operating current                  | IOP                   | COMP=2V, FB pin pull<br>150uA, CS=1V,<br>GATE=1nF to GND | 1    | 1.4  | 2.5  | mA   |  |

| Burst working mode current                    | I <sub>BURST</sub>    | COMP=0V, GATE=1nF to GND                                 | 200  | 280  | 400  | uA   |  |

| VCC hold threshold                            | V <sub>CC_HOLD</sub>  |                                                          | 7    | 8.3  | 9.5  | V    |  |

| VCC overvoltage protection threshold          | V <sub>CC_OVP</sub>   |                                                          | 89   | 93   |      | V    |  |

| VCC clamp threshold                           | V <sub>CC_CLAMP</sub> |                                                          |      | 1 03 |      | V    |  |

| Closed loop control (CC                       | MP pin)               |                                                          |      | l    | I    |      |  |

| COMP open loop voltage                        | V <sub>COMP_OP</sub>  | C OMP pin open circuit                                   |      | 4.4  |      | V    |  |

| COMP short circuit current                    | ICOMP_SHORT           | COMP =0V                                                 | 100  | 160  | 250  | u A  |  |

| Burst mode entry threshold                    | V <sub>BM_ET</sub>    |                                                          | 0.3  | 0.34 | 0.4  | V    |  |

| Burst Mode hysteresis voltage                            | V <sub>BM_HY</sub>     |           | 0.02 | 0.05       | 0.09 | V      |

|----------------------------------------------------------|------------------------|-----------|------|------------|------|--------|

| OPP over power protection threshold                      | V <sub>OPP</sub>       |           | 2.8  | 3          | 3.2  | V      |

| OPP deglitch time (1)                                    | T <sub>D_OPP</sub>     |           |      | Tss *6     |      | ms     |

| The ratio of COMP to CS                                  | Avcs                   |           | 2.3  | 2.5        | 2.7  | V/V    |

| Slope compensation voltage                               | V <sub>SLOPE</sub>     | Duty =75% |      | 0.3        | (    | V      |

| Current detection part (                                 | CS pin)                |           |      |            | (    |        |

| Soft start time                                          | TSS                    |           | 4    | <i>z</i> C | 10   | m s    |

| leading edge blanking time                               | T <sub>LEB</sub>       |           |      | 2 80       |      | ns     |

| Rectifier short circuit protection threshold (OC FAULT)  | V <sub>SR_SH</sub>     |           | 1.1  | 1.2        | 1.3  | V      |

| Rectifier short circuit protection triggering period (1) | T <sub>SR -SH</sub>    |           |      | 3          |      | Cycles |

| Cycle-by-Cycle Maximum Current Limit                     | V <sub>CS_CBC</sub>    | 1         | 0.7  | 0.77       | 0.84 | V      |

| Auxiliary winding voltage                                | je detection (         | FB pin)   |      |            |      |        |

| Valley detection current threshold                       | I <sub>FB_VALLEY</sub> | OL,       |      | 1 0        |      | u A    |

| Brown in current threshold                               | IB .                   |           | 82   | 94         | 106  | uA     |

| Brown out current threshold                              | I <sub>BNO</sub>       |           | 74   | 85         | 96   | u A    |

| Brown out blanking time                                  | T <sub>BL_BNO</sub>    |           |      | Tss *7     |      | ms     |

| Output overvoltage protection threshold                  | $V_{FB\_OVP}$          |           | 3.3  | 3.6        | 3.9  | V      |

| Output overvoltage protection blanking time              | T <sub>BL_OVP</sub>    |           |      | 7          |      | cycles |

| Output short circuit protection threshold                | V <sub>FB_ST</sub>     |           | 0.15 | 0.2        | 0.25 | V      |

| Output short circuit protection shielding time           | T <sub>BL_ST</sub>     |           |      | 7          |      | cycles |

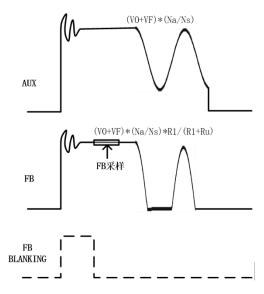

| FB sampling time                                         | T <sub>SAMPL</sub>     | CS=0.5V   |      | 1.1        |      | us     |

| FB high judgment threshold                               | $V_{FB\_H}$            |           | 1.7  | 1.9        | 2.1  | V      |

| FB medium judgment threshold               | V <sub>FB_M</sub>                   |                             | 0.9      | 1   | 1.1 | V            |

|--------------------------------------------|-------------------------------------|-----------------------------|----------|-----|-----|--------------|

| Driver section                             |                                     |                             |          |     |     |              |

| Drive low level voltage                    | V <sub>G_L</sub>                    |                             |          |     | 0.5 | V            |

| Drive high level voltage                   | $V_{G_{\underline{\hspace{1pt}}}H}$ | VCC=13 V, Gate<br>Load=20mA | 8        |     |     | ٧            |

| Drive high level clamping voltage          | V <sub>G_HC</sub>                   | VCC=V <sub>CC_OVP</sub>     |          | 11  |     | V            |

| Drive rise time                            | T <sub>R</sub>                      | Cload =1nF                  |          | 210 | (   | n s          |

| Drive down time                            | T <sub>F</sub>                      | Cload =1nF                  |          | 30  |     | n s          |

| Control section                            |                                     |                             | <u>I</u> |     |     |              |

| Normal operating frequency                 | F <sub>SW_NOM</sub>                 |                             | 60       | 65  | 70  | kHz          |

| Energy saving mode working frequency       | F <sub>SW_GREEN</sub>               |                             |          | 25  |     | kHz          |

| Frequency jitter range (1)                 |                                     |                             | (0)      | ±6  |     | %            |

| Frequency jitter period (1)                |                                     |                             | 0,       | 8   |     | ms           |

| Maximum duty cycle                         | D <sub>MAX</sub>                    | (8)                         | 74       | 77  | 80  | %            |

| Over temperature protection (1)            | T <sub>HSD</sub>                    | 0,                          |          | 155 |     | $^{\circ}$ C |

| Over temperature protection hysteresis (1) | T <sub>HSD_HYS</sub>                | 14                          |          | 30  |     | $^{\circ}$ C |

#### Note:

(1) Values are verified by characterization on bench, not tested in production.

# 9. Pin Function

| Pin number | Pin name | ne describe                             |  |

|------------|----------|-----------------------------------------|--|

| 1          | GND      | land                                    |  |

| 2          | COMP     | Voltage feedback input pin              |  |

| 3          | FB       | Auxiliary winding voltage detection pin |  |

| 4          | CS       | Current sense input pin                 |  |

| 5          | VCC      | Power supply                            |  |

| 6          | OUT      | Drive output pin                        |  |

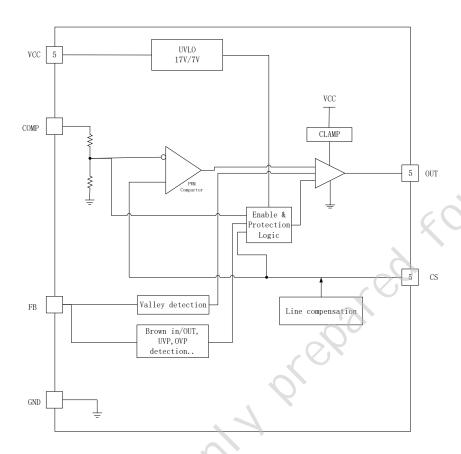

# 10. Internal Functional Block Diagram

Figure 1 Internal functional block diagram

## 11. Function Description

#### **Power Supply Starts**

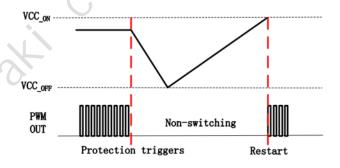

During startup, the bus capacitor charges the chip's VCC via the startup resistor. Since the startup current of the chip is very small (approximately five µA), a larger resistance can be selected to minimize standby losses. Additionally, startup delay should also be considered when selecting the resistance value. Once VCC reaches the turn-on voltage (VCC\_ON), the chip begins to emit pulses.

#### **Soft Start**

During the start-up process, because the output voltage is very low, if the frequency and CS voltage are not controlled, the chip will try to operate at the maximum switching frequency and maximum peak current due to the effect of the loop, which will cause the system to operate at a very deep CCM, bringing higher stress on the primary and secondary sides. MK2687 adopts multi-stage control to optimize the primary and secondary stress during startup.

#### **Operating Curve**

For PD applications, the chip has different operating frequency curves at different output voltages. The chip detects the FB pin voltage during the secondary side freewheeling period to determine the output voltage and adopts different frequency curves to optimize the efficiency at each output voltage point.

In order to improve the EMI impact, the chip also employs a dithering technique, where the frequency is distributed within a  $\pm 6\%$  range.

## Input Undervoltage Recovery (Brown In)

During the power-on process, the PWM controller sends out a series of narrow pulses, in which the BROWN IN detection is completed. During the turn-on process of the primary MOS, the voltage of FB pin is about 0V. At this time, the current flowing out of the FB pin =  $\frac{V_{BULK}*Na}{Ru*Np}$ , Only when this current is greater than  $I_{BNI}$ , the

chip will consider that the BROWN IN condition has been met and start up normally.

If the BROWN-IN condition is not met, the chip enters the restart process after the narrow pulses

### Input Undervoltage (Brown Out)

During normal operation, the chip is always in the primary side MOS opening process, detecting the outflow FB current. When the outflow current < I  $_{\text{BNO}}$  and the duration  $\geq$  T  $_{\text{BL\_BNO}}$ , the bus voltage is considered undervoltage, it will turn off the drive voltage. The chip enters the restart process.

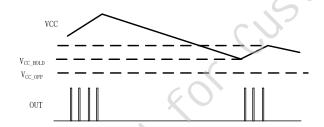

#### **Vcc Power Supply Hold**

When operating under a particularly light load with an extremely low output voltage, the VCC voltage approximates Na \* Vo/Ns. Should the switching frequency be significantly low, VCC voltage may decrease substantially. To address this, the chip includes a power supply hold mode. This mode activates when VCC voltage falls to the VCC\_HOLD threshold, compelling the chip to generate pulses to prevent VCC from dropping into the shutdown range. Due to these

forced pulses, VCC voltage will begin to rise again. Once it reaches approximately 9.5V, the chip will cease forced pulsing.

However, in system design, it is preferable to maintain the VCC voltage consistently above  $V_{\text{CC\_HOLD}}$  by optimizing the VCC capacitance, the turns ratio of the auxiliary winding, and the minimum load. This strategy helps avoid the activation of the power supply hold mode, which can disrupt loop regulation and cause the output voltage to increase, potentially increasing ripple.

#### **Control Mechanism**

MK2687 is current mode PWM controller with cycle-by-cycle current limit. The switching current is detected by a sense resistor at CS pin. An internal leading-edge blanking circuit with blanking time (T<sub>LEB</sub>) blocks the sensed voltage spikes at initial power MOSFET ON state due to snubber diode reverse recovery and surge gate current at power MOSFET. The maximum cycle-by-cycle current limit is set by V<sub>CS\_CBC</sub>/RCS.

MK2687 also clamps the maximum duty cycle to  $D_{\text{MAX}}$ . Once the  $D_{\text{MAX}}$  duty cycle is reached, the output turns off.

#### **Input Line Compensation**

MK2687 uses the detected input line voltage through the current at FB pin ( $I_{FB}$ ) to generate the current going out of CS pin with external line compensation resistor  $R_{LR}$  to achieve more constant actual peak current regardless of line voltage.

### **Internal Slope Compensation**

The chip includes built-in slope compensation circuitry, which adds a linear ramp to the current sense input voltage. This ramp is proportional to the duty cycle and is used for PWM (Pulse Width Modulation) generation. This feature significantly enhances closed-loop stability when operating in Continuous Conduction Mode (CCM). It also prevents subharmonic oscillation, which in turn reduces output ripple.

#### Voltage Feedback Loop

The COMP pin serves as the voltage loop feedback input and is connected to the output of a TL431 voltage reference via an optocoupler. It functions by comparing this feedback voltage with the current signal to generate the drive signal for the circuit.

For optimal loop performance and easier debugging, it is recommended to place a ceramic capacitor in parallel with the resistor that is connected in series with the diode on the secondary side of the optocoupler. This configuration can help stabilize the feedback signal and improve the overall response of the feedback loop.

# Auxiliary Winding Voltage detection (FB voltage Detection)

During the freewheeling phase of the secondary side current, the voltage on the FB pin represents a fractional voltage from the auxiliary winding. This fraction indirectly reflects the output voltage.

The FB voltage is sampled during the transformer's demagnetization period and compared against predefined thresholds to enable several critical functions:

#### **Output Over-voltage Protection**

If the FB voltage sensed exceeds V<sub>FB\_OVP</sub>, the output over-voltage protection is triggered to safeguard against excessively high voltages.

#### **Output Short Circuit Protection (Vout UVP)**

If the FB voltage sensed is lower than  $V_{\text{FB\_ST}}$  for seven consecutive cycles, protection occurs, and the chip enters restart.

#### **Efficiency Optimization**

The detected output voltage and comp voltage determine the control curve, optimizing the system's efficiency based on real-time operational conditions.

#### **Valley Switching**

After secondary side rectification process is done, the drain voltage starts oscillating with a frequency of approximately  $1/2 \text{ m}\sqrt{(\text{Coss}\times\text{Lp})}$ , where Lp is the inductance of primary winding of the transformer and COSS is capacitance on the drain of primary MOSFET. When the oscillation ringing is below 0V at auxiliary winding, the chip clamps FB pin to ~0V, and senses the current at FB pin. When the current out of FB reaches a design value, a "possible" valley is locked and MK2687L turns on after propagation delay.

#### **Protective Function**

Reliable power supply system is achieved with auto-recovery protections including cycle-by-cycle current limit and output over-current protection (OCP), over-power-protection (OPP), output over-voltage protection, etc. Detailed protection features are described in the following sessions.

| Mk2687 Protection<br>Function                  | Mk2687 Protection<br>Mechanism |

|------------------------------------------------|--------------------------------|

| Overpower Protection                           | Restart                        |

| Output Overvoltage<br>Protection               | Restart                        |

| Vcc Overvoltage<br>Protection                  | Restart                        |

| Cs Short Circuit Protection                    | Restart                        |

| Synchronous Rectifier Short Circuit Protection | Restart                        |

| Output Short Circuit Protection                | Restart                        |

#### **Overpower Protection (OPP)**

The chip implements over power protection (OPP) by monitoring the voltage at the COMP pin. If the COMP voltage exceeds the set overpower threshold (V<sub>OPP</sub>) and remains above this threshold for a duration longer than six times the soft-start time (T<sub>SS</sub> \* 6), the chip interprets this condition as an overload situation. In response, OPP is activated, and the chip initiates a restart process to prevent damage and ensure safe operation.

## **Cycle-by-cycle Current Limit**

The current-mode control IC compares the CS signal with the COMP cycle by cycle, but when the output is short-circuited or the optocoupler is open, the COMP voltage may rise extremely high, resulting in excessive IPK current and causing transformer saturation. Therefore, the chip adds an addition protection level, the CS voltage will be compared with V<sub>CS\_CBC</sub> (~0.77V) cycle by cycle. After the blanking time TLEB, as long as the CS reaches VCS\_CBC, the chip will chop drive signal immediately.

# Secondary Side Sr Short Circuit Protection (sscp)

In the event of a short circuit in the secondary side synchronous rectifier, the peak current through the power MOSFET increases sharply upon activation. To address this, the chip is designed for rapid response. When the CS pin detects a voltage exceeding the predefined V<sub>SR\_SH</sub> threshold, the current sense blanking time is immediately reduced to 90ns. This allows the power MOSFET to be turned off instantaneously within the same switching cycle. If such conditions persist across three consecutive switching cycles, the chip activates its auto-recovery SSCP mode to safeguard the system effectively.

## **Vcc Overvoltage Protection**

When VCC reaches  $V_{\text{CC\_OVP}}$ , the chip immediately stops driving output and enters the restart process.

## **Over Temperature Protection (OTP)**

The chip features built-in over-temperature protection that activates at a preset threshold

ONFII DENILI O

temperature  $(T_{HSD})$  and includes a hysteresis temperature  $(T_{HSD\_HYS})$  to prevent frequent toggling of the protection state.

Additionally, customers can enhance OTP by integrating an external Negative Temperature Coefficient (NTC) resistor into the CS pin circuit. As the board temperature increases, the resistance of the NTC resistor decreases. Should the voltage at the CS pin (VCS) exceed the critical baseline value (V<sub>CS\_CBC</sub>) and this condition persists for fifteen consecutive cycles, the OTP is triggered. Following this, the chip initiates an auto-recovery process to protect the system under excessive temperature conditions.

#### **Other Protection Features**

There are several critical protections designed in the MK2687L to prevent the power supply at fault state. In case listed below, MK2687L will trigger protection:

- 1. Adjacent PINS short

- 2. PINS open

- 3. CS short

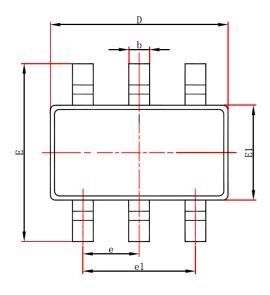

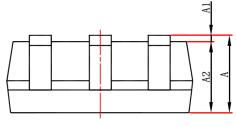

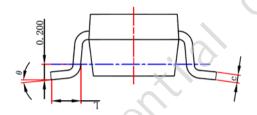

# 12. Package Size (SOT23-6)

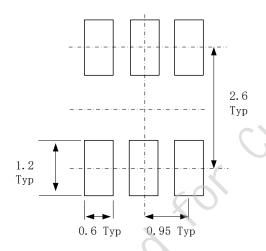

#### **Recommended Land Pattern**

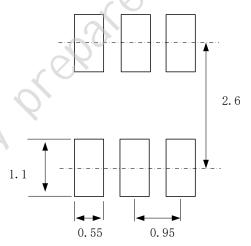

**Recommended Stencil Openings**

| Ch     | Dimensions Ir | n Millimeters | Dimensions | In Inches<br>Max. |  |

|--------|---------------|---------------|------------|-------------------|--|

| Symbol | Min.          | Max.          | Min.       |                   |  |

| A      | 1.050         | 1.250         | 0.041      | 0.049             |  |

| A1     | 0.000         | 0.100         | 0.000      | 0.004             |  |

| A2     | 1.050         | 1.150         | 0.041      | 0.045             |  |

| b      | 0.300         | 0.500         | 0.012      | 0.020             |  |

| С      | 0.100         | 0.200         | 0.004      | 0.008             |  |

| D      | 2.820         | 3.020         | 0.111      | 0.119             |  |

| E1     | 1.500         | 1.700         | 0.059      | 0.067             |  |

| E      | 2.650         | 2.950         | 0.104      | 0.116             |  |

| е      | 0.950         | (BSC)         | 0.037      | (BSC)             |  |

| e1     | 1.800         | 2.000         | 0.071      | 0.079             |  |

| L      | 0.300         | 0.600         | 0.012      | 0.024             |  |

| θ      | 0°            | 8°            | 0°         | 8°                |  |