### 45V/18mΩ, SYNCHRONOUS RECTIFICATION SWITCHER

## 1. Description

The MK1706 is a compact secondary side synchronous rectification switcher which integrated controller and MOSFET for high performance flyback converters. It is compatible with DCM and QR operations.

The MK1706 can generate its own supply voltage while with high-side rectification; this eliminates the need of auxiliary winding of the transformer, which is usually required to produce supply voltage.

While in low-side rectification, the external circuit could be very simple with no other components and VCC connected to Vout directly.

The MK1706 offers the proprietary circuit to avoid potential false turn-on during DCM and QR operations. This feature eliminates the need of minimum off time for SR gate and makes system more reliable.

The precise zero voltage turn off allows the maximum synchronous rectification of MOSFET conduction time for the high efficiency design.

# 2. Typical Applications

- 5V Output AC/DC Adapters

- 5V Output Standby and Auxiliary power supplies

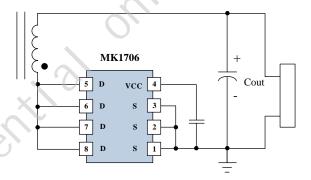

# 4. Simplified Application

Used in high side rectification

#### 3. Features

- Integrated 18mΩ 45V Power MOSFET

- Optimized for 5V2A-2.4A applications to meet DOE VI and CoCV5 Tier2 compliance

- Operates in a wide output voltage range down to 3V voltage (self-supply)

- Self-supply for operations with low-side rectification and high-side rectification without an auxiliary winding

- No need of external capacitor in low side with Vout bias configuration

- Advanced Output Voltage monitor to work with Dynamic Load Response Acceleration features of PSR controllers, which improves transient response and/or reduces output capacitor value

- Discharges VCC in OVP to protect Interface

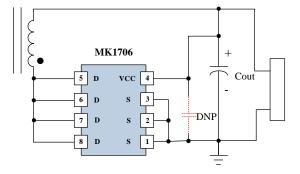

IC in low side configuration with Vout bias

- Supports DCM and QR Operations

- Precise 0V turn off for maximum efficiency

- Designed for <150kHz working frequency</li>

- <1mW power dissipation in standby</p>

- Excellent 4kV HBM ESD tolerance

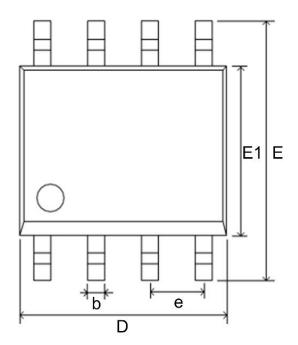

- Available in SOP-8 Package

Used in low side rectification

## 5. Ordering Information

| Ordering No. | Description          |  |

|--------------|----------------------|--|

| MK1706CBR    | SOP-8, 4000 pcs/reel |  |

# 6. Package Reference

XXXXXXXXX: Lot code

SOP-8

| Absolute Maximum Ratings (1)                                  | Recommended Operation Conditions         |                         |  |

|---------------------------------------------------------------|------------------------------------------|-------------------------|--|

| VCC to S0.3V to $+8V(T_J = +25^{\circ}C)$                     | VCC to S                                 |                         |  |

| D to S1V to +45V                                              | D to S                                   | -0.7V to 40V            |  |

| Continuous drain current I <sub>D</sub> 7A <sup>(2)</sup>     | Maximum Junction Temp. (T <sub>J</sub> ) | +125°C                  |  |

| Pulsed drain current I <sub>DM</sub> 28A <sup>(3)</sup>       | , <del>,</del> ,                         |                         |  |

| Continuous Power Dissipation.2.5W (Ta = +25°C) <sup>(4)</sup> | Thermal Resistance (5)                   | $\theta$ JA $\theta$ JC |  |

| Junction Temperature150°C                                     | SOP-8 80                                 | 35 °C/W                 |  |

#### Notes:

- (1) Exceeding these ratings may damage the device.

- (2) Ta=25  $^{\circ}\text{C}$  ; Calculated continuous current based on maximum allowable junction temperature

- (3) Repetitive rating: pulse width limited by maximum junction temperature

- (4) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub>(MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub>(MAX)=(T<sub>J</sub>(MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will cause excessive die temperature.

- (5) Measured on JESDSD51-7, 4 layers PCB

## 7. Esd Ratings

|                            |                                                                               | Value | Units |

|----------------------------|-------------------------------------------------------------------------------|-------|-------|

| Electrostatic              | Human body model (HBM), per ANSI/ESDA/JEDEC JS 001, all pins <sup>(1)</sup>   | 4000  | V     |

| discharge V <sub>ESD</sub> | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | 1750  | V     |

#### Notes:

- (1) JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process

- (2) JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process

## 8. Electrical Characteristics

### T<sub>A</sub>=25°C, unless otherwise noted.

| Parameter                                             | Symbol                 | Conditions                | Min      | Тур  | Max | Units |

|-------------------------------------------------------|------------------------|---------------------------|----------|------|-----|-------|

| Internal Mos Section                                  |                        |                           |          | •    |     |       |

| Internal MOS Rdson                                    | R <sub>dson</sub>      | VCC=5.9V, Id=0.5A         |          | 18   |     | mΩ    |

| Drain to Source Breakdown                             | V <sub>DSS(BR)</sub>   | VCC=5V, Id=2mA            | 45       |      |     | VX    |

| Supply Management Section                             |                        |                           |          |      |     | .5    |

| VCC UVLO Rising                                       | Vcc_on                 |                           | 2.75     |      |     | V     |

| VCC UVLO Falling                                      | Vcc_off                |                           | 2.5      |      | 1   | V     |

| VCC UVLO Hysteresis                                   | Vcc_hyst               |                           |          | 0.3  |     | V     |

| VCC Regulation Voltage                                | Vcc_reg                | V <sub>D</sub> = 7.5V     |          | 5    |     | V     |

|                                                       |                        | VCC=5V,                   |          | 2.2  |     | Λ     |

| Operating Current                                     | Icc                    | Fsw=100KHz,               |          | 2.3  |     | mA    |

|                                                       |                        | VCC=5V, Fsw=1KHz          |          | 0.15 |     | mA    |

| Quiescent Current                                     | I <sub>q(VCC)</sub>    | VCC=5V, Fsw=0Hz           |          | 70   |     | μΑ    |

| VCC Discharging voltage(OVP)                          | V <sub>CC_dis</sub>    |                           | <b>.</b> | 6.3  |     | V     |

| VCC Discharging current(OVP)                          | I <sub>VCC_dis</sub>   |                           | Q        | 30   |     | mA    |

| CONTrol Circuitry Section                             |                        | (0                        |          |      |     |       |

| Turn-On Threshold (V <sub>D</sub> -V <sub>SS</sub> )  | $V_{\text{ON\_th}}$    | 0,                        | -300     | -200 |     | mV    |

| Turn Off Threshold (V <sub>D</sub> -V <sub>SS</sub> ) | $V_{OFF\_th}$          |                           |          | 0    |     | mV    |

| Turn-On Propagation Delay                             | $T_{D\_on}$            |                           |          | 20   |     | ns    |

| Turn-Off Propagation Delay                            | $T_{D\_off}$           |                           |          | 20   |     | ns    |

| Turn On Blanking Time                                 | T <sub>B_ON</sub>      | C <sub>LOAD</sub> = 2.2nF |          | 1.3  |     | μs    |

| Dira Section                                          |                        |                           |          |      |     |       |

| Internal trigger threshold_relative                   | VDLRA_trig             |                           |          | 0.16 |     | ٧     |

| Internal trigger threshold_abs                        | V <sub>DLRA_trig</sub> |                           |          | 4.75 |     | V     |

| Blanking time after SR off to                         | T <sub>DLRA_bla</sub>  |                           |          | 00   |     | _     |

| enable DLRA trigger                                   | nk                     |                           |          | 66   |     | us    |

| Gate Driver Section                                   | Gate Driver Section    |                           |          |      |     |       |

| Gate driver output low voltage                        | $V_{G\_LOW}$           |                           | 0        |      | 0.2 | V     |

| Gate driver output high voltage                       | $V_{G\_HIGH}$          |                           |          | 5    |     | V     |

## 9. Pin Functions

| Pin #   | Name | Description                                            |  |

|---------|------|--------------------------------------------------------|--|

| 1,2,3   | S    | Ground, also used as FET source sense reference for VD |  |

| 4       | VCC  | Inner Regulator Output, supply MK1706                  |  |

| 5,6,7,8 | D    | FET drain voltage sense; Internal LDO input            |  |

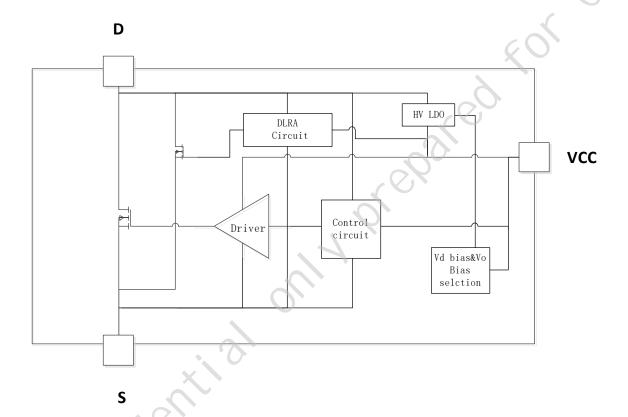

## 10. Block Diagram

Figure 1. Functional Block Diagram

### 11. Operation Descriptions

MK1706 is a high performance synchronous rectifier which can replace the Schottky diode rectification in the flyback converter to improve efficiency. A great flexibility for system designing is brought by Self-supply which supports operations with both low-side rectification and high–side rectification without an auxiliary winding.

#### **Vcc and Startup**

MK1706 can be biased by two ways. One way is to power from D pin through the internal LDO. The other way is to use Vout to supply in low side configuration which bypass the internal LDO. MK1706 is intelligently determine whether to bias from internal LDO during system startup. The VCC OVP protection is included in MK1706. The current IVCC\_dis(typical 30mA) discharges VCC when VCC exceeds VCC\_dis(typical 6.3V). This feature protects Vout OVP also when VCC is connecting to Vout directly.

#### **Turn on Phase**

MK1706 uses its proprietary pre-determine method to prevent from falsely turn-on by DCM ringing. 20ns turn on propagation delay and -200mV turn on threshold also reduce the body diode conduction time on turn-on phase.

#### **Turn on Blanking Time**

After SR VG goes to high, a turn on blanking time is needed to ensure the parasitic ringing does not falsely trigger SR VG to turn off. The turn on blanking time of MK1706 is ~1.3us.

#### **Turn off Phase**

When SR VG goes to high, the conduction resistance of internal MOSFET would be very small. Vds increases to zero according to the decrease of SR MOSFET current lsd. Finally Vds reaches to V<sub>OFF\_th</sub> (0V), and MK1706 turns off the internal MOSFET within as short as 20ns.

#### **DIra(Dynamic Load Response Acceleration) Function**

A drawback for PSR (Primary side control) controller is the poor load transient response in light load. MK1706 is capable to monitor the situations of Vout by monitoring Vds voltage, and wakeup PSR controllers to improve the load transient performance if the PSR controllers have the wakeup functions. MK1706 uses a controlled MOS to change the impedance between Drain and source to produce voltage disturbance transmitted to primary side.

## 12. Typical Implementations

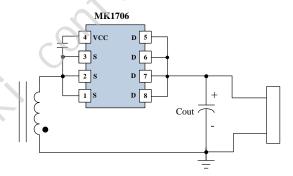

MK1706 supports high side rectification to replace Schottky diode without the need of auxiliary winding as shown in Figure 2. In this configuration, VCC is powered from pin D and regulated at ~5.2V even when Vout is much lower than 5V in CC mode or short mode.

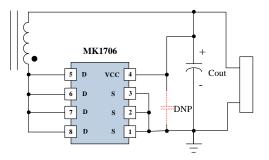

There are two configurations for MK1706 in low side rectification. When VCC is connected to a 0.1uF to 1uF cap as in Figure 3, VCC is powered from pin D and regulated at ~5.2V as same as in high side rectification.

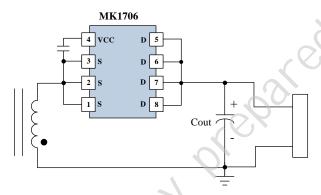

The other configuration in low side rectification is to connect VCC to Vout+ directly to bypass the internal LDO as shown in Figure 4. The decoupling cap could be eliminated if the PCB layout is good and the VCC wire is short. In this configuration, VCC always equal to Vout+ that means when Vout drop to  $V_{CC\_OFF}$ , MK1706 enters VCC UVLO and uses body diode to rectify. Considering the effect of ripple of output voltage, MK1706 might enter into VCC UVLO when Vout drop to 3.5V.

Figure 2. The High side rectification

Figure 3. The low side rectification (1)

Figure 4.The low side rectification (2)

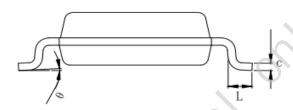

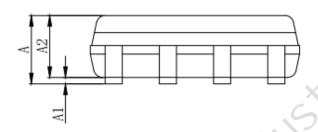

# 13. Package Information (SOP-8)

**TOP VIEW**

SIDE VIEW

**FRONT VIEW**

| Symbol | Dimensions In Millimeters |      |  |  |

|--------|---------------------------|------|--|--|

| Symbol | MIN                       | MAX  |  |  |

| Α      | 1.3                       | 1.75 |  |  |

| A1     | 0.05                      | 0.25 |  |  |

| A2     | 1.25                      | 1.65 |  |  |

| b      | 0.33                      | 0.51 |  |  |

| С      | 0.2                       | 0.25 |  |  |

| D      | 4.7                       | 5.1  |  |  |

| E      | 5.8                       | 6.2  |  |  |

| E1     | 3.8                       | 4.0  |  |  |

| е      | 1.270(BSC)                |      |  |  |

| L      | 0.4                       | 1.27 |  |  |

| θ      | 0°                        | 8°   |  |  |