# 100V Input, 1A, Ultra-Low IQ, Synchronous Buck Converter

### 1. Description

The MK9018 operates over a wide input voltage range from 5V to 100V. With integrated the main MOSFET and a synchronous MOSFET, the MK9018 delivers up to 1A output current.

The MK9018 adopts a constant on-time (COT) control architecture to achieve excellent transient response.

With patented standby circuits, the device can achieve ultra-low  $I_Q$ , and exit the standby mode fast.

### 2. Applications

- BMS (E-Bike, Electric Tools)

- Automotive and Industry Systems

- Motor Drives, Telecom

#### 3. Features

- Wide Input Voltage 5V-100V

- 1A Output Current Capability

- Low RDS(ON) for Internal MOSFETS 500mΩ/250mΩ

- <100µA Supply Current under ILOAD=100µA</li>

- MK9018FAD Adjustable FSW up to 1MHz

- Internal 3ms Soft-start

- Smart power saving and ultra-Fast Transient Response

- Precision ±1% Feedback Reference

- Open-Drain Power Good Indicator

- OC, OT Protection with Hiccup Mode

- No Loop Compensation Components

- ESOP8 Package with Thermal PAD

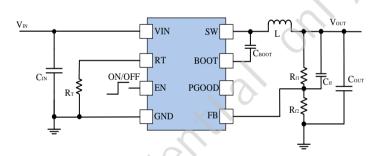

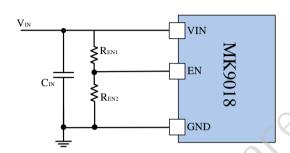

## 4. Typical Application

Figure 1. Typical Application Diagram

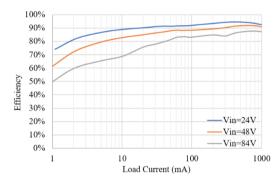

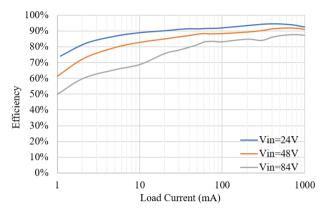

Figure 2. Efficiency at 5Vout

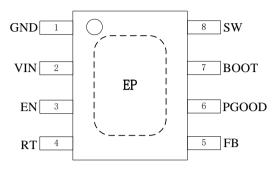

# 5. Package Reference and Pin Function

ESOP8(top view)

|           | \ 8 SW                |

|-----------|-----------------------|

| VIN 2 EP  | 7 BOOT                |

| EN 3      | 6 PGOOD               |

| RT 4      | 5 FB                  |

| ESOP8( t  | cop view)             |

| Order No. | Description           |

| MK9018FAD | ESOP-8, tape, 4k/reel |

| Pin # | Name        | Description                                                                                                                                                                                          |

|-------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | GND         | Ground pin.                                                                                                                                                                                          |

| 2     | VIN         | Input pin. Decouple this pin to GND with a low ESR ceramic capacitor.                                                                                                                                |

| 3     | EN          | Enable control pin. The device has accurate 1.17V rising threshold and a programable falling threshold. This pin also can be used for programming the VIN turn on voltage with the resistor divider. |

| 4     | RT          | On-time programming pin. A resistor between this pin and GND sets the buck switch on-time. $F_{SW}(kHz) = \frac{3.2 \times Vout(V)}{R_T(M\Omega)}$                                                   |

| 5     | FB          | Output feedback pin. Connect this pin to the center point of the output resister divider to program the output voltage: $V_{OUT}=1.2\times(1+R_{f1}/R_{f2})$                                         |

| 6     | PGOOD       | Power good indicator pin. This pin is an open-drain output pin. Connect to a source voltage through an pull-up resistor.                                                                             |

| 7     | BOOT        | Boot-strap pin. Decouple this pin to SW pin with a 10nF ceramic capacitor.                                                                                                                           |

| 8     | SW          | Inductor pin. Connect to the switch node of the power inductor.                                                                                                                                      |

| EP    | Thermal PAD | Exposed pad of the package. Solder the EP to the GND pin and connect to a large copper plane to reduce thermal resistance.                                                                           |

## 6. Absolute Maximum Ratings (1)

| VIN, EN, SW to GND                                                    | 0.3V to 110V  |

|-----------------------------------------------------------------------|---------------|

| SW to GND (20ns pulse)                                                | 3V to 110V    |

| BS to GND                                                             | SW+6.6V       |

| RT to GND                                                             |               |

| FB to GND ·····                                                       |               |

| PGOOD to GND                                                          |               |

| Power Dissipation, P <sub>D</sub> @T <sub>A</sub> =25°C, ESOP8 ······ | 3.3W          |

| Package Thermal Resistance                                            |               |

| $	heta_{JA}$ (Junction to ambient)                                    | 30°C/W        |

| $	heta_{JC}$ (Junction to case)                                       | ······10℃/W   |

| Operating Junction Temperature, TJ                                    | 40°C to 160°C |

| Storage Temperature, T <sub>stg</sub> ······                          | 65℃ to 160℃   |

| Soldering Temperature(10 second), T <sub>sld</sub>                    | ,260℃         |

#### Note:

(1) Stresses beyond the "ABSOLUTE MAXIMUM RATINGS" may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated in "RECOMMENED OPERATING CONDITIONS". Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## 7. Recommended Operating Conditions

| VIN Voltage ······             | <br>5V to 100V   |

|--------------------------------|------------------|

|                                |                  |

| CMAN / II                      | 0.001            |

| SW Voltage                     | <br>0.3V to 100V |

| Operating Junction Temperature | <br>             |

# 8. ESD Ratings

| 0                          | Value                                                                                             | Units |          |

|----------------------------|---------------------------------------------------------------------------------------------------|-------|----------|

| Electrostatic              | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, SW, BOOT, EN, RT, FB, PGOOD (1).              | ±2000 | >        |

| discharge V <sub>ESD</sub> | Charged device model (CDM), per JEDEC specification JESD22-C101, SW, BOOT, EN, RT, FB, PGOOD (2). | ±500  | <b>V</b> |

#### Notes:

- (1) JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process

- (2) JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process

#### 9. Electrical Characteristics

$V_{\text{IN}}$ =24V,  $V_{\text{OUT}}$ =5V, L=47 $\mu$ H,  $C_{\text{OUT}}$ =22uF. Typical values correspond to  $T_{\text{J}}$ =25 $^{\circ}$ C, Minimum and Maximum limits apply over the full -40 $^{\circ}$ C to 125 $^{\circ}$ C junction temperature range unless otherwise indicated.

| <b>Paramete</b>      | r                                         | Test Conditions                                          | MIN   | TYP  | MAX      | UNIT         |

|----------------------|-------------------------------------------|----------------------------------------------------------|-------|------|----------|--------------|

| Input Volt           | age                                       |                                                          |       |      |          |              |

| VIN                  | Input Voltage                             |                                                          | 5     |      | 100      | V            |

| Supply Co            | urrent                                    |                                                          |       |      | l .      |              |

| Ishutdown            | Shutdown Current                          | V <sub>EN</sub> =0V                                      |       | 7.7  |          | μA           |

| ISTANDBY             | Standby Current                           | V <sub>EN</sub> =V <sub>IN</sub> , I <sub>OUT</sub> =0A, |       | 65   |          | μA           |

| Feedback             |                                           |                                                          |       |      |          |              |

| V <sub>REF</sub>     | Feedback reference voltage                |                                                          | 1.182 | 1.2  | 1.218    | V            |

| EN/UVLO              | -                                         |                                                          |       | X    | )        | I            |

| V <sub>ENH</sub>     | EN rising threshold                       | V <sub>IN</sub> =48V, I <sub>OUT</sub> =0.6A             | 1.0   | 1.17 | 1.24     | V            |

| I <sub>EN</sub>      | Hysteresis Input Current                  | V <sub>IN</sub> =48V, I <sub>OUT</sub> =0.6A             | 1     | -1.6 | -2.2     | μΑ           |

| Hysteresis           |                                           |                                                          |       |      |          |              |

| PGOOD                |                                           |                                                          |       | ı    | I        | ı            |

| $V_{PGH}$            | FB rising threshold for PGOOD low to high | V <sub>FB</sub> rising                                   | 1.05  | 1.15 | 1.25     | V            |

| $V_{PGL}$            | FB falling threshold for PGOOD            | V <sub>FB</sub> falling                                  | 0.95  | 1.05 | 1.15     | V            |

| F                    | high to low                               |                                                          |       |      |          |              |

| Frequenc             |                                           | 2.2-1/ (1)                                               | 1     | 1    | <u> </u> | Ī            |

| Fsw                  | Programmable Switching Frequency Range    | $F(kHz) = \frac{3.2xV_{OUT}(V)}{R_T(M\Omega)}$           | 100   |      | 1000     | kHz          |

| Timing               |                                           |                                                          |       |      |          |              |

| t <sub>ON-MIN</sub>  | Minimum on-time                           |                                                          |       | 50   |          | ns           |

| t <sub>OFF-MIN</sub> | Minimum off-time                          |                                                          |       | 270  |          | ns           |

| Power Sw             | vitches                                   |                                                          |       |      |          |              |

| R <sub>DSON-HS</sub> | High-side MOSFET RDSON                    | Only tested at T <sub>J</sub> =25℃                       |       | 0.5  | 0.6      | Ω            |

| R <sub>DSON-LS</sub> | Low-side MOSFET RDSON                     | Only tested at T <sub>J</sub> =25℃                       |       | 0.25 | 0.35     | Ω            |

| Current L            | imit                                      |                                                          |       |      | I .      | I            |

| I <sub>PEAK-HS</sub> | High-side MOSFET Peak Current limit       | Only tested at T <sub>J</sub> =25℃                       | 1.6   |      | 2.4      | Α            |

| Ivalley-ls           | Low-side MOSFET Valley                    | Only tested at                                           | 0.8   | 1    | 1.2      | A            |

| <i>J</i> *           | Current limit                             | TJ=25℃                                                   |       | -    |          |              |

| Soft Start           |                                           |                                                          | T     | 1 -  | ı        | ı            |

| tss                  | Soft-start time                           |                                                          |       | 3    |          | ms           |

| Thermal S            |                                           |                                                          | T     | T    | I        | 1 .          |

| T <sub>SD</sub>      | Thermal Shutdown Threshold                | T∍rising                                                 |       | 160  |          | $^{\circ}$   |

| Thys                 | Thermal Shutdown Hysteresis               |                                                          |       | 25   | <u> </u> | $^{\circ}$ C |

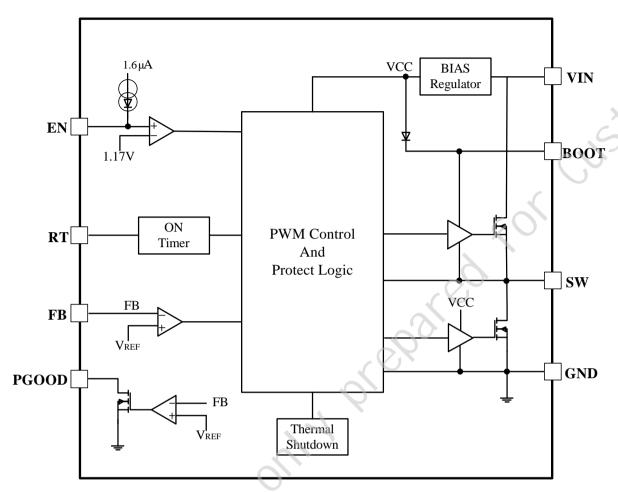

# 10. Block Diagram

Figure 3. Block Diagram

## 11. Typical Characteristics

Figure 4. Efficiency at 12Vout

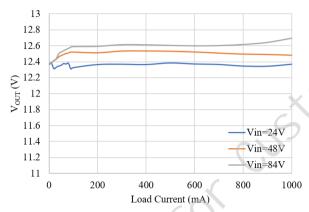

Figure 5. Load and Line Regulation

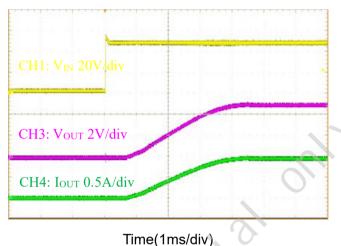

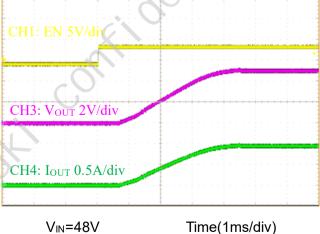

Figure 6. Startup from VIN

Time(1ms/div)

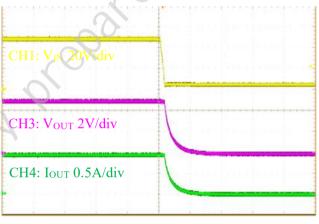

Figure7. Shutdown from VIN

V<sub>IN</sub>=48V Time(1ms/div) **Figure9. Shutdown from EN**

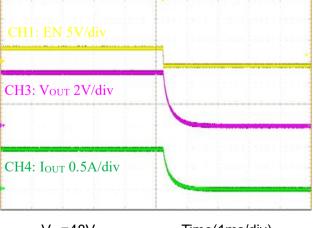

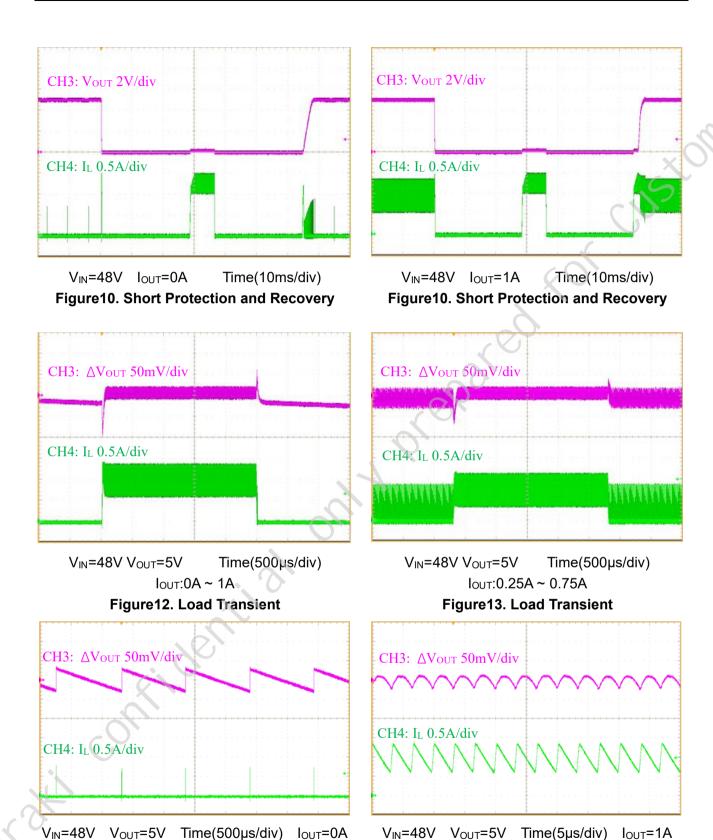

Figure 14. Out Ripple

Figure 15. Out Ripple

#### 12. Applications

#### 12.1 Operation Overview

The MK9018 is a ultra-low  $I_Q$  synchronous buck converter. With very low  $R_{DS(ON)}$  MOSFETs, the MK9018 can achieve very high efficiency. This converter operates over a wide input voltage range from 4.5V to 100V delivering up to 1A DC load current. As adopting constant on-time (COT) mode, MK9018 can achieve fast transient responses for high voltage step down applications. Control loop compensation is not required for this regulator, reducing design time and external component count. And the pin arrangement is designed for a simple layout requiring only a few external components.

Because of high integration in the MK9018, the application circuit is very simple. Only the on-timer resister  $R_T$ , the feedback resistors ( $R_{fl}$  and  $R_{fl}$ ), the BOOT capacitor  $C_{BOOT}$ , the feedforward capacitor  $C_{fl}$ , the input capacitor  $C_{IN}$ , the output capacitor  $C_{OUT}$  and the output inductor L need to be selected for the targeted applications.

#### 12.2 Switching Frequency (R<sub>T</sub>)

The switch frequency of MK9018 is set by the on-time resistor RT. As shown below, in  $5V_{OUT}$  application a  $43k\Omega$  resistor sets the switching frequency at 300kHz.

$$F_{SW}(kHz) = \frac{3.2 \times V_{OUT}(V)}{R_T(M\Omega)}$$

Note that the final switching frequency is not only affected by component tolerant but also  $t_{\text{ON-MIN}}$  and  $t_{\text{OFF-MIN}}$ .

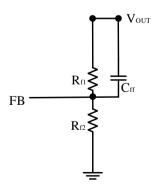

#### 12.3 Output Voltage Program

Choose  $R_{f1}$  and  $R_{f2}$  to program the output voltage. For target  $V_{OUT}$  setpoint, calculate Rf1 and Rf2 using below equation:

$$V_{OUT} = 1.2V \times (1 + \frac{R_{f1}}{R_{f2}})$$

$R_{f1}$  in the range of  $100k\Omega$  to  $500k\Omega$  is recommended for most applications. Larger feedback resistors consumes less DC current, which is important if light-load efficiency is critical. But too large resistors is not recommended as the feedback path would become more susceptible.

The feedforward capacitor  $C_{\rm ff}$  is strongly recommended, which can improve the system stability and transient responses.

#### 12.4 Input Capacitor (C<sub>IN</sub>)

An input capacitor is necessary to limit the input ripple voltage while providing AC current to the buck converter at every switching cycle. The input ripple voltage  $\Delta V_{IN}$  at input capacitor is calculated as:

$$\Delta V_{IN} = \frac{I_{OUT} \times D \times (1 - D)}{F_{SW} \times C_{IN}} + I_{OUT} \times R_{ESR}$$

The capacitance of input capacitor is calculated as

$$C_{IN} \geq \frac{I_{OUT} \times D \times (1 - D)}{F_{SW} \times (\Delta V_{IN} - I_{OUT} \times R_{ESR})}$$

To minimize the potential noise problem, a X5R or better grade capacitor with sufficient voltage rating is recommended. This capacitor should be close to the VIN and GND pins to minimize the loop area formed by  $C_{IN}$  and VIN/GND pins. In this application, a  $1\mu F$  low ESR ceramic capacitor is recommended.

#### 12.5 Output Inductor (L)

It is recommended to choose the ripple current of inductor between 30% to 50% of the rated load current  $I_{OUT}(max)$  for most applications. The inductance is calculated as:

$$L = \frac{V_{OUT}}{F_{SW} \times \Delta I_L} \times (1 - \frac{V_{OUT}}{V_{IN}})$$

And the peak current of inductor is calculated as:

alculated as:

$$I_L(\text{peak}) = I_{OUT}(max) + \frac{\Delta I_L}{2}$$

The saturation current rating of the inductor must greater than the  $I_L$ (peak). An inductor whose saturation current is above the current limit setting of the MK9018 will be best choice. Note that inductor saturation current levels generally decrease as the inductor temperature increase.

#### 12.6 Output Capacitor (Cout)

The output capacitor limits the capacitive voltage ripple at the converter output. This voltage ripple which is generated from the triangular inductor current ripple flowing into and out of the capacitor can be calculated as:

$$\Delta V_{OUT} = \frac{\Delta I_L}{8 \times F_{SW} \times C_{OUT}}$$

Above equation only take the steady state ripple into consideration. The transient requirements also must be taken into consideration when selecting the output capacitor. The X5R or better grade ceramic capacitor larger than 22µF is recommended.

#### 12.7 Enable Operation

Input UVLO can be programmed by EN rising threshold. The UVLO turn-on voltage can be calculated as:

$$V_{UVLO} = (1 + \frac{R_{EN1}}{R_{EN2}}) \times V_{ENH}$$

V<sub>ENH</sub> is EN rising threshold voltage, typical is 1.17V.

The UVLO hysteresis is accomplished with an internal 1.6µA current source that is switched on or off into the impedance of the set-point divider. When the voltage at the EN pin exceeds the rising threshold, the current source is activated to quickly raise the voltage at the EN pin. The hysteresis can be calculated as:

$$V_{hvs}(V) = R_{EN1} \times 1.6 \mu A$$

#### 12.8 Boot-strap capacitor

This capacitor provides the energy for high-side gate driver. A high quality 10nF ceramic capacitor connected between the BS pin and the SW pin is recommended. Also a RC series net can be used for slow down the turn-on speed of high side MOSFET.

## 12.9 Power Good (PGOOD)

MK9018 provides a PGOOD flag pin to indicate whether the output voltage is within the regulation level. PGOOD is an open-drain output that requires a pullup resistor to a DC source. The typical range of pullup resistance is about  $10k\Omega$ . When the FB voltage exceeds 96% of the reference, the internal switch will be turned off and PGOOD can be pulled high by the pullup resistor. If the FB voltage falls below 92% of the reference, the switch will be turned on and PGOOD is pulled low to indicate the output voltage is out of regulation.

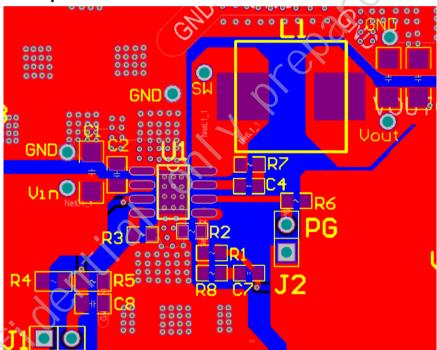

#### 13. Layout

#### 13.1 Layout Guideline

To achieve high performance of the MK9018, the following layout tips must be followed.

- (1) At least one low-ESR ceramic bypass capacitor  $C_{IN}$  must be used. Place the  $C_{IN}$  as close as possible to the MK9018 VIN and GND pins.

- (2) Minimize the loop area formed by C<sub>IN</sub> connections to VIN and GND pins.

- (3) Inductor must be placed close to the SW pin. Minimize the area of SW trace to avoid the potential noise problem.

- (4) Maximize the PCB area connecting to the GND pin and thermal pad. If it is allowed, a ground plane can be used as noise shielding and heat dissipation path.

- (5) Place the feedback resistors, R<sub>f1</sub> and R<sub>f2</sub>, close to the FB pin. Route the feedback V<sub>OUT</sub> sense path away from noisy nodes such as the SW net.

- (6) The RT pin is sensitive to noise. The on-time set resistor R<sub>T</sub> must be close to the device.

## 13.2 Layout Example

Figure 16. Layout Example

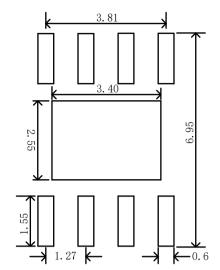

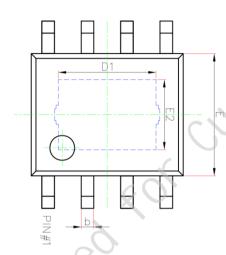

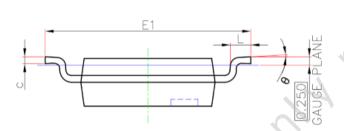

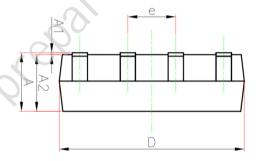

## 14. Package Size

Figure 17. Recommended Land Pattern (mm)

Figure 18. MK9018 Top View

Figure 19. MK9018 Side View

Figure 20. MK 9018 Side View

| SYMBOL   | Millimeter |       |  |  |  |

|----------|------------|-------|--|--|--|

| STIVIDOL | MIN        | NOM   |  |  |  |

| Α        | 1.300      | 1.700 |  |  |  |

| A1       | 0.000      | 0.100 |  |  |  |

| A2       | 1.350      | 1.550 |  |  |  |

| b        | 0.330      | 0.510 |  |  |  |

| С        | 0.170      | 0.250 |  |  |  |

| D        | 4.700      | 5.100 |  |  |  |

| D1       | 3.050      | 3.250 |  |  |  |

| Е        | 3.800      | 4.000 |  |  |  |

| E1       | 5.800      | 6.200 |  |  |  |

| E2       | 2.160      | 2.360 |  |  |  |

| е        | 1.270(BSC) |       |  |  |  |

| L        | 0.400      | 1.270 |  |  |  |

| θ        | 0°         | 8°    |  |  |  |

Cheroller

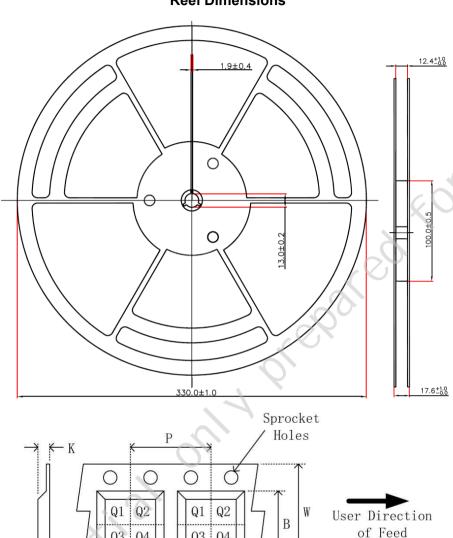

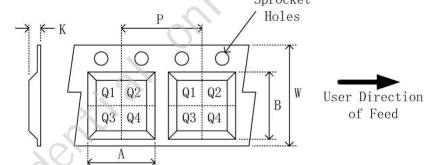

# 15. Reel and Tape Information

#### **Reel Dimensions**

| Device    | Package | Pins | SPQ   | Α       | В       | K       | Р     | W      | Pin1     |

|-----------|---------|------|-------|---------|---------|---------|-------|--------|----------|

| Device    | Type    |      | (pcs) | (mm)    | (mm)    | (mm)    | (mm)  | (mm)   | Quadrant |

| MK9018FAD | ESOP-8  | 8    | 4000  | 6.5±0.1 | 5.4±0.1 | 2.0±0.1 | 8±0.1 | 12±0.1 | Q1       |

## 16. Tape and Reel Box Dimensions

| Device    | Package | Pins  | SPQ   | Length | Width | Height |

|-----------|---------|-------|-------|--------|-------|--------|

| Device    | Туре    | FIIIS | (pcs) | (mm)   | (mm)  | (mm)   |

| MK9018FAD | ESOP-8  | 8     | 8000  | 360    | 360   | 65     |