# Single-Port IEEE 802.3af/at PSE Controller

# 1. Description

The MK3614T is a high-density integrated autonomous single Ethernet port power sourcing equipment (PSE) controller designed for use in IEEE 802.3af/at Power over Ethernet (PoE) systems. The device provides powered device (PD) detection, classification, current limit, load disconnect detection, and operating current levels. The device features intelligent protection circuitry and allows the delivered to PD power up to 30W. The device integrates a  $0.3\Omega$  power MOSFET and a current-sensing resistor, which enables the non-PoE protocol adapter to be feasibly retrofitted into a PSE adapter with the PoE protocol only requiring a few external components.

The MK3614T's LED pin is an open-drain output. The pin outputs simple digital logic signals, which indicate various operating statuses and fault conditions. The device supports Midspan or Endpoint mode. The Midspan mode function has a longer detection back-off timer.

# 2. Applications

- IEEE 802.3af and 802.3at Power-Sourcing Equipment (PSE)

- Power over Ethernet Switches/Routers

- IP Phone Systems

- IP Camera Systems

- 5G Small Cells

### 3. Features

- IEEE 802.3af and 802.3at compatible

- Fully autonomous operation, no external controller required

- Up to 30W for PSE Applications

- 0.2mA standby current (Midspan mode)

- Integrated an 80V 0.3Ω power MOSFET and current-sensing resistor

- Multi-point detection

- Class 3 and Class 4 configuration

- Supports reset operation

- LED status indication

- Supports Midspan and Endpoint modes

- 8-pin ESOP-8 package with thermal pad

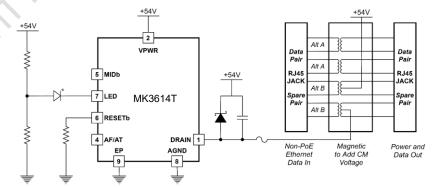

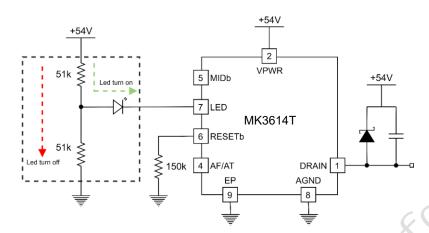

# 4. Typical Application

Figure 1. Typical Application Diagram for 802.3at Midspan Configuration

# 5. Order Information

| Order Part Number | Descriptions          |

|-------------------|-----------------------|

| MK3614TGAD        | ESOP-8, tape, 4k/reel |

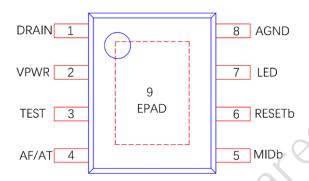

# 6. Pin Configuration and Functions

Figure 2. Pin Function (top view)

**Table 1. Pin Functions**

|   | Pin |                    | I/O                                                     | Description                                                                                                                                                       |

|---|-----|--------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ı | NO. | Name               |                                                         |                                                                                                                                                                   |

|   | 1   | DRAIN              | Analog Power<br>Output                                  | MOSFET drain output.                                                                                                                                              |

|   | 2   | VPWR               | Analog Power Input                                      | Positive PoE voltage (+44V to 57V) relative to AGND.                                                                                                              |

|   | 3   | TEST               | -                                                       | Connect to AGND.                                                                                                                                                  |

|   | 4   | AF/AT              | Digital Input                                           | Pull up to internal VDD rail with 10µA current. Connect to AGND                                                                                                   |

|   |     |                    | X                                                       | for AF configuration, leave floating for AT configuration.                                                                                                        |

|   | 5   | MIDb               | Digital Input                                           | Pull up to internal VDD rail with 10µA current. Connect to AGND to set 2.7 seconds detection backoff timing (Midspan), leave floating for Endpoint configuration. |

|   | 6   | RESETb             | Digital Input                                           | Pull up to internal VDD rail with $20\mu A$ current. Active low device reset input. Connect a $120k\Omega$ to $200k\Omega$ resistor to AGND.                      |

|   | 7-  | LED Digital Output |                                                         | Open drain output pin, turn on an external LED when a PoE PD is connected and powered. Refer to LED section for more details.                                     |

|   | 8   | AGND               | Analog Ground                                           | Analog ground.                                                                                                                                                    |

|   | 9   | EPAD               | Exposed pad, it should be connected to AGND, connect to |                                                                                                                                                                   |

# 7. Specifications

### 7.1 Absolute Maximum Ratings (1)

|                                                     |                                      | MIN  | MAX | Units      |

|-----------------------------------------------------|--------------------------------------|------|-----|------------|

|                                                     | VCC VPWR, DRAIN to<br>AGND           | -0.3 | 80  |            |

| Input voltages                                      | LED to AGND                          | -0.3 | 35  | V          |

|                                                     | TEST, AF/AT, RESETb,<br>MIDb to AGND | -0.3 | 7   | 5          |

| Operating Junction Temperature,                     |                                      | -40  | 150 |            |

| Storage Temperature, T <sub>stg</sub>               |                                      | -65  | 160 | $^{\circ}$ |

| Soldering Temperature (10 second), T <sub>sld</sub> |                                      | 660  | 260 |            |

### Note:

(1) Stresses beyond the "ABSOLUTE MAXIMUM RATINGS" may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated in "RECOMMENDED OPERATING CONDITIONS". Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                            | · · · · · · · · · · · · · · · · · · ·                                          |      | Units |

|----------------------------|--------------------------------------------------------------------------------|------|-------|

| Electrostatic              | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001                             | 500  | V     |

| discharge V <sub>ESD</sub> | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | 2000 | V     |

### Notes:

- JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process

- JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process

### 7.3 Recommended Operating Conditions

|                                  |                                 | MIN | MAX  | Units |

|----------------------------------|---------------------------------|-----|------|-------|

|                                  | VPWR, DRAIN to AGND             | 32  | 60   |       |

| Recommended Operation Conditions | LED to AGND                     | 0   | 30   | \ \ \ |

|                                  | TEST, AF/AT, MIDb, RESETb, MIDb | 0   | 5.5  | V     |

|                                  | to AGND                         |     |      | (     |

|                                  | Junction Temperature            | -40 | +125 | ~°C   |

### 7.4 Thermal Information

|                            |                                     | Value | Units |

|----------------------------|-------------------------------------|-------|-------|

| Package Thermal Resistance | $\theta_{JA}$ (Junction to ambient) | 30    | °C/W  |

|                            | $\theta_{JC}$ (Junction to case)    | 10    | 5,11  |

### 7.5 Electrical Characteristics

Conditions are -40°C < T<sub>J</sub> < 125 °C, V<sub>PWR</sub> = 54 V unless otherwise noted. Typical values are at 25 °C. All voltages are with respect to AGND unless otherwise noted.

| Parameter                           |                                              | Test Conditions                                                              | MIN  | TYP  | MAX  | UNIT |

|-------------------------------------|----------------------------------------------|------------------------------------------------------------------------------|------|------|------|------|

| Power Supply Volta                  | ages                                         |                                                                              |      |      |      |      |

| Vuvlo_on                            | V <sub>PWR</sub> UVLO Input<br>Voltage       |                                                                              | 25.5 | 28   |      | V    |

| Vuvlo_off                           | V <sub>PWR</sub> UVLO Input<br>Voltage       |                                                                              |      | 31   | 33.5 | >    |

| Power Supply Curr                   | ents <sup>(1)</sup>                          |                                                                              |      | 6    | O.,  |      |

| lpwr                                | V <sub>PWR</sub> Supply                      | During normal operation (Detection + Idle), MIDb=Float                       | _    | 0.45 | _    | mA   |

| IPWK                                | Current                                      | During normal operation (Detection + Idle), MIDb=GND                         | 56   | 0.2  | _    | mA   |

| Detection Specifica                 | ations                                       |                                                                              | O-   |      |      |      |

| I <sub>DET_SC</sub>                 | Detection Short<br>Circuit Current           | Measured when DRAIN is shorted to VPWR                                       | -    | 1.5  | 5    | mA   |

| V <sub>PORT</sub>                   | Detection Voltage When R <sub>DET</sub> = 24 | V <sub>PWR</sub> - V <sub>DRAIN</sub> , primary detection voltage            | 2.8  | 4    |      | V    |

|                                     | kΩ                                           | V <sub>PWR</sub> - V <sub>DRAIN</sub> , secondary detection voltage          | 1    | 8    | 10   | V    |

| T <sub>DET</sub>                    | Detection Time                               |                                                                              | _    | 320  | 500  | ms   |

| T <sub>IDLE</sub>                   | Detection Idle                               | MIDb=Float                                                                   | _    | 315  | _    | ms   |

| TIDLE                               | Time                                         | MIDb=GND                                                                     | _    | 2700 | _    | ms   |

| R <sub>GOOD</sub> <sup>(1)</sup>    | Signature<br>Resistance                      |                                                                              |      | 25   | -    | kΩ   |

| R <sub>DET_MIN</sub> <sup>(1)</sup> | Minimum<br>Signature<br>Resistance @ PD      |                                                                              | 15   | 17   | 19   | kΩ   |

| R <sub>DET_MAX</sub> <sup>(1)</sup> | Maximum<br>Signature<br>Resistance @ PD      |                                                                              | 26.5 | 30   | 33   | kΩ   |

| Скејест                             | Reject Signature<br>Capacitance              |                                                                              | _    | 2.2  | 10   | μF   |

| Classification Spec                 | cifications                                  |                                                                              |      |      |      |      |

| VCLASS                              | Class Event<br>Voltage                       | V <sub>PWR</sub> - V <sub>DRAIN</sub> , Class current<br>between 0 and 51 mA | 15.5 | _    | 20.5 | V    |

|                       | Class Event                     | Measured when DRAIN is                               |     |          |     |        |

|-----------------------|---------------------------------|------------------------------------------------------|-----|----------|-----|--------|

| Iclass_lim            | Class Event  Current Limitation | shorted to VPWR                                      | 51  | _        | 95  | mA     |

|                       |                                 |                                                      |     |          |     |        |

| T <sub>CLE</sub>      | Class Event                     | Assigned PD Class 0, 1, 2, 3,                        | 6   |          | 30  | ms     |

|                       | Timing                          | 4                                                    | _   |          | _   |        |

|                       |                                 | Class Signature 0                                    | 0   | _        | 5   | mA     |

|                       |                                 | Threshold between Class                              | 5   |          | 8   | mA     |

|                       |                                 | Signature 0 or 1                                     |     |          |     |        |

|                       |                                 | Class Signature 1                                    | 8   |          | 13  | mA     |

|                       |                                 | Threshold between Class                              | 13  |          | 16  | mA     |

|                       |                                 | Signature 1 or 2                                     | 10  |          |     | 1117 ( |

|                       | 01:6:                           | Class Signature 2                                    | 16  |          | 21  | mA     |

| ICLASS_REGION         | Classification                  | Threshold between Class                              | 24  |          | 25  | A      |

|                       | Current Region                  | Signature 2 or 3                                     | 21  | <u> </u> | 25  | mA     |

|                       |                                 | Class Signature 3                                    | 25  | _        | 31  | mA     |

|                       |                                 | Threshold between Class                              | 7   |          |     |        |

|                       |                                 | Signature 3 or 4                                     | 31  | _        | 35  | mA     |

|                       |                                 | Class Signature 4                                    | 35  | _        | 45  | mA     |

|                       |                                 | Threshold between Class                              |     |          |     |        |

|                       |                                 | Signature 4 or invalid Class                         | 45  | _        | 51  | mA     |

| Classification Mark   | Specifications                  |                                                      |     |          |     |        |

|                       | Mark Event                      | V <sub>PWR</sub> - V <sub>DRAIN</sub> , Mark current | 7   |          | 10  |        |

| Vmark                 | Voltage                         | between 0 and 5 mA                                   |     | _        |     | V      |

|                       | Mark Event                      | Measured when DRAIN is                               |     |          |     |        |

| I <sub>MARK_LIM</sub> | Current Limitation              | shorted to VPWR                                      | 51  | _        | 95  | mA     |

|                       | Mark Event                      | v shorted to VI VVIC                                 |     |          |     |        |

| T <sub>ME</sub>       | Timing                          | Assigned PD Class 4                                  | 6   | _        | 12  | ms     |

| Current Limit and 0   |                                 |                                                      |     |          |     |        |

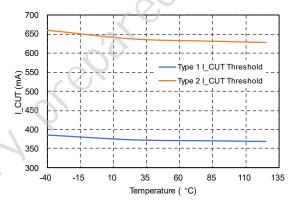

| Current Limit and     |                                 | TA=25°C, AF/AT=0b                                    | 350 | 375      | 400 | mΛ     |

| Ісит                  | Overcurrent                     |                                                      |     |          |     | mA     |

|                       | Threshold                       | TA=25°C, AF/AT=1b                                    | 600 | 640      | 680 | mA     |

| Тсит                  | Overcurrent Time                |                                                      | 50  | _        | 75  | ms     |

| -0)                   | Limit                           |                                                      |     |          |     |        |

|                       | Output Current in               | TA=25°C, all assigned PD                             |     |          |     |        |

| Inrush                | POWER_UP                        | Classes, V <sub>PORT</sub> > 30 V                    | _   | 425      | _   | mA     |

|                       | State                           | ,                                                    |     |          |     |        |

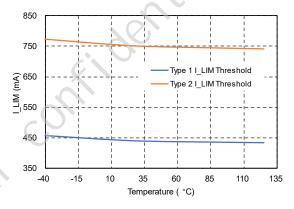

|                       |                                 | TA=25°C, Power-on, assigned                          | 405 |          | _   | mA     |

| ILIM                  | Current Limit                   | PD Class 0, 1, 2, 3                                  | 100 |          |     |        |

| ILIM                  | Ourient Linnit                  | TA=25°C, Power-on, assigned                          | 685 |          | _   | mA     |

|                       |                                 | PD Class 4                                           | 000 |          |     | 11171  |

| _                                     | Short Circuit Time           | Power-on, assigned PD Class 0, 1, 2, 3   | 50  | _   | 75  | ms            |

|---------------------------------------|------------------------------|------------------------------------------|-----|-----|-----|---------------|

| Тым                                   | Limit                        | Power-on, assigned PD Class 4            | 10  | _   | 75  | ms            |

| Load Disconnect                       |                              |                                          |     |     |     | •             |

| IPORT_DIS                             | DC MPS Current               | Current per pairset                      | _   | 7.5 | 10  | mA            |

| T <sub>MPDO</sub>                     | PD MPS Dropout<br>Time Limit |                                          | 300 | _   | 400 | ms            |

| MOSFET On Resis                       | tance                        |                                          |     |     | 5   |               |

| R <sub>DSON</sub>                     | FET Resistance               | 100mA drain to source current            |     | 290 |     | mΩ            |

| Digital Pin Characteristics           |                              |                                          |     |     |     |               |

| VIL                                   | Input Low Voltage            | AF/AT, RESETb, MIDb                      |     |     | 1   | V             |

| V <sub>IH</sub>                       | Input High Voltage           | AF/AT, RESETb, MIDb                      | 2   | 5   |     | V             |

| ILK                                   | Input Leakage                | AGND < VIN < VDD, AF/AT,<br>RESETb, MIDb | -1  | _   | 1   | μA            |

| l <sub>PU</sub>                       | Pullup Current to<br>VDD     | AF/AT, MIDb = 0V                         | -13 | -10 | -7  | μΑ            |

| l <sub>PU</sub>                       | Pullup Current to<br>VDD     | RESETb = 0V                              | -26 | -20 | -14 | μΑ            |

| Over Temperature                      | Protection (1)               |                                          |     |     |     |               |

| T <sub>RISE</sub>                     | Rising Threshold             |                                          | _   | 150 | _   | $^{\circ}$    |

| TFALL                                 | Recover<br>Threshold         | 0,                                       | _   | 130 | _   | ${\mathbb C}$ |

| · · · · · · · · · · · · · · · · · · · |                              | · · · · · · · · · · · · · · · · · · ·    |     |     |     |               |

### Note:

<sup>(1)</sup> Values are verified by characterization on bench, not tested in production.

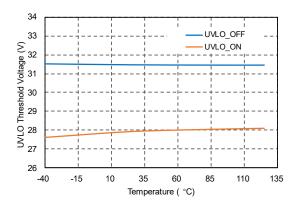

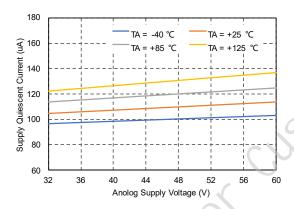

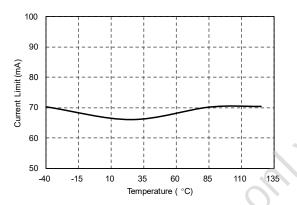

# 7.6 Typical Characteristics

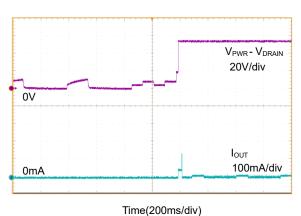

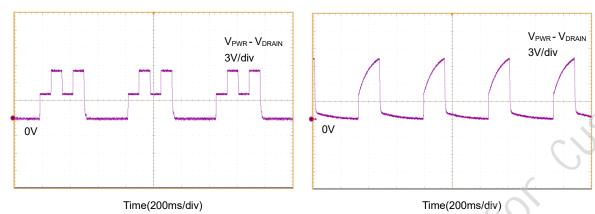

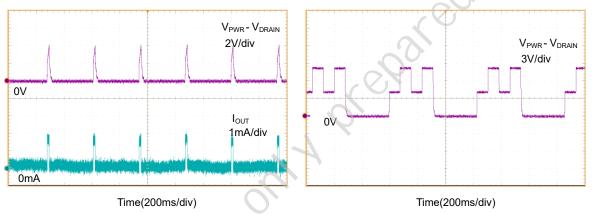

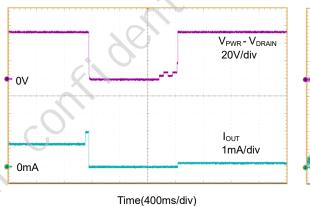

Typical values are at  $V_{PWR}$  = 54V, TA = 25°C, Endpoint mode with a Class 0 PD, unless otherwise noted.

Figure 3. V<sub>PWR</sub> UVLO Threshold Voltage vs. Temperature

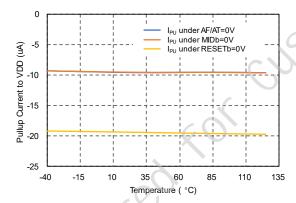

Figure 4. Digital Pin Pullup Current to VDD

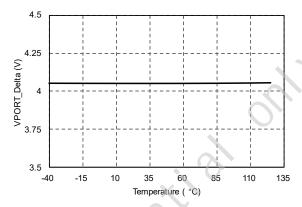

Figure 5. Voltage Difference Between Detection Points vs. Temperature

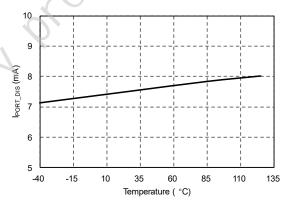

Figure 6. DC Maintain Power Signature

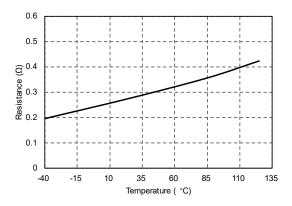

Figure 7. Internal FET Resistance vs.

Temperature

Figure 8. VPWR Current vs. Temperature (RESETb = 0V)

Figure 9. Classification and Mark Current Limit vs. Temperature

Figure 10. Overcurrent Threshold vs.

Temperature

Figure 11. Current Limit Threshold vs.

Temperature

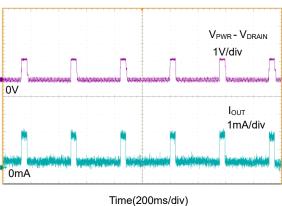

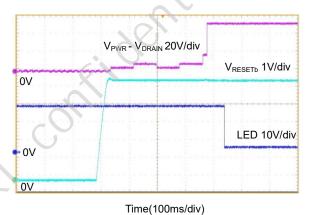

Figure 12. Startup with a valid PD

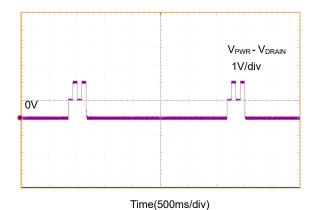

Figure 13. Detection with invalid PD (33k $\Omega$ )

Figure 14. Detection with invalid PD (Open)

Figure 15. Detection with invalid PD (24k $\Omega$  and 10 $\mu$ F)

Figure 16. Detection with invalid PD (15 $k\Omega$ )

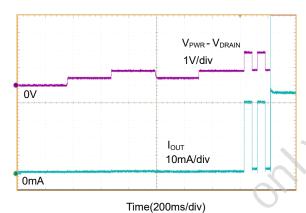

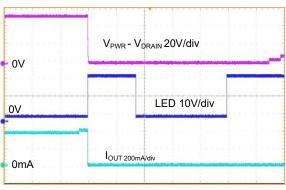

Figure 17. Overcurrent restart delay

Figure 18. Detection with output shorted

MK3614T v1.0 Specifications Subject to Change without notice www.meraki-ic.com © 2024 Meraki IC.

0V

Class 3

I<sub>OUT</sub>

Class 2

Class 1

Class 0

Figure 19. Detection in Midspan with invalid PD (15kΩ)

Figure 20. Classification with different PD classes (0 to 3)

Time(200ms/div)

Figure 21. Classification with PD Class 4

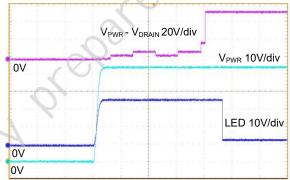

Figure 22. LED function of the PD powered from  $\ensuremath{V_{\text{PWR}}}$

Time(100ms/div)

Figure 23. LED function of the PD powered from V<sub>RESETb</sub>

Figure 24. LED function of ICUT

Time(200ms/div)

MK3614T v1.0 Specifications Subject to Change without notice www.meraki-ic.com © 2024 Meraki IC.

# 8. Detailed Description

### 8.1 Overview

The MK3614T is a high-density integrated autonomous single-port PSE controller designed for use in IEEE 802.3af/at PoE systems. The device provides PD detection, classification, current limit, load disconnect detection and operating current levels. The MK3614T provides up to 30W to the Ethernet port. Besides, the MK3614T features intelligent protection circuitry including input undervoltage lockout, over-temperature protection, overcurrent timeout, port short protection, load-disconnect detection timeout, port voltage slew-rate limit during startup, operating status, fault conditions indicated by LED.

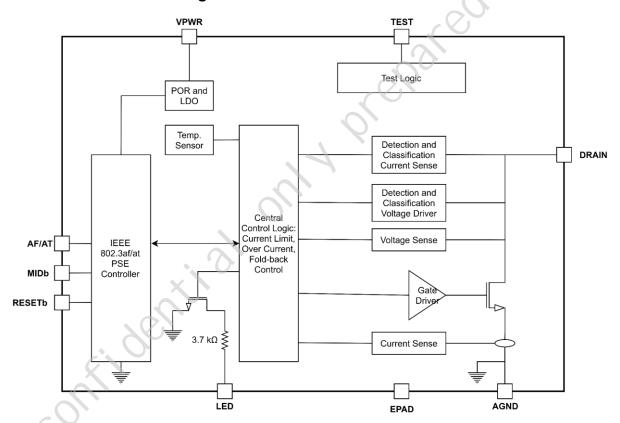

### 8.2 Functional Block Diagram

Figure 25. Block Diagram

### 8.3 Feature Description

#### 8.3.1 Reset

The MK3614T is reset by power-up and hardware reset. Reset condition is cleared once V<sub>PWR</sub> rises above the UVLO threshold. The MK3614T's RESETb pin is tied to internal VDD through a pull-up resistance. In a typical application, connect a 120k $\Omega$  to 200k $\Omega$  resister to AGND. However, if the RESETb pin is driven low (> 110us, typ), the MK3614T is reset. Once in the reset state, the port output and LED detection function are disabled. At the end of a reset event, the MK3614T latches in the state of AF/AT and MIDb input signals. During normal operation, changes of the AF/AT and MIDb inputs are ignored, and these inputs can only be changed at any time prior to the end of a reset state.

#### 8.3.2 Midspan Mode

The MK3614T supports an Endpoint or Midspan PSE network configuration. In midspan mode, when failed detections occur, the device waits about 2.7s before attempting to detect again. Like the RESETb pin, MIDb pin is also tied to internal VDD through a pull-up resistance. The device is configured as Endpoint mode by default unless the MIDb pin is driven low.

#### 8.3.3 **PD Detection and Classification**

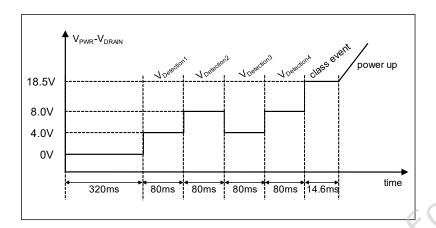

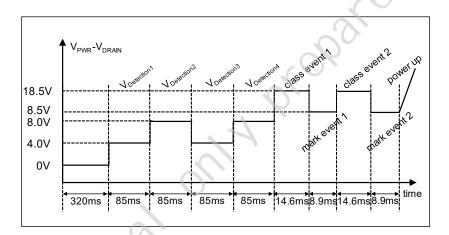

Detection function of the MK3614T is the most important, which determines if the remote equipment connected to a PSE is capable of receiving power. To avoid false detection in noisy environments, the MK3614T detects a PD by using a robust 4-point detection algorithm to reliably determine the signature resistance of the PD. During detection phase, the MK3614T keeps the internal MOSFET off and drives probe voltages with two different levels through the DRAIN pin. The device uses a specific algorithm to calculate the PD signature resistance by sampling the current injected into the port. Once the detection result is RGOOD, the MK3614T will perform Physical Layer classification by driving a class probe to determine the PD's class signature. The number of class events and mark events determines the PD requested power. Figure 26 shows a timing diagram of PD detection and classification for a Type 1 PSE powering a Type 1 PD. In this example, the MK3614T produces one class event to a Type 1 PD without any mark event. As shown in Figure 27, two class events and two mark events are driven by the MK3614T for a Type 2 PSE powering a Class 4 PD.

JIS COME!

Figure 26. Type 1 Detection, Classification, and Port Power-Up Sequence

Figure 27. Type 2 Detection, Classification, and Port Power-Up Sequence

### 8.3.4 Inrush

After classification, if the MK3614T decides to power the PD, it will first go through the inrush phase. During inrush, the PSE limits the amount of current being delivered for at least 60ms. Between 1ms and 60ms after power-on, the inrush current of the MK3614T is limited to no more than 450mA

### 8.3.5 Operating Power

During a nominal powering state, the MK3614T checks for abnormal conditions, including overcurrent, PD disconnection, and short-circuits. Meanwhile, the MK3614T assigns the class required for PD to PD. The MK3614T achieves the purpose of distributing power by controlling the current called I<sub>CUT</sub>. Once the current exceeds the I<sub>CUT</sub> as least T<sub>CUT</sub>, the MK3614T immediately cuts off the power and goes through detection phase.

MK3614T v1.0 www.meraki-ic.com 14

#### 8.3.6 **Maintain Power Signature**

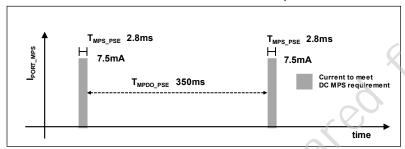

When the MK3614T is supplying power to a PD, the MK3614T keeps on monitoring the current drawn in order to make sure that the PD is still connected. The minimum current that the PD must draw to avoid being disconnected is named the Maintain Power Signature (MPS). The MK3614T is designed to remove power when the MPS is absent for at least 350ms, ensuring that disconnected cables do not remain powered. In order to further reduce minimum standby power consumption for PoE systems, the MK3614T only requires that PD must draw a current above I<sub>PORT DIS</sub> for at least 2.8ms with no more than T<sub>MPDO</sub> between pulses.

Figure 28. The MK3614T MPS requirements

#### **Current Limit and Voltage Foldback** 8.3.7

The MK3614T integrates a current-sensing resistor connected between the internal MOSFET and AGND to monitor the loop current. During normal operating conditions, the current running through the current-sensing resistor never exceeds the threshold ILIM. Otherwise, the internal feedback circuit regulates the driver voltage of the MOSFET to limit the current. Besides, the MK3614T senses the DRAIN voltage and regulates the current-limit value, which helps to reduce the internal MOSFET power dissipation.

#### 8.3.8 **LED Signals**

The MK3614T's LED pin is open-drain output. The pin outputs simple digital logic signals, which indicate various operating statuses and fault conditions. The LED pin can be directly connected to the VIN port through pull -up resistors, but an external pull-down resistor is required to reduce the voltage stress of the LED pin. As shown in Figure 25, the LED pin outputs various signals by controlling the internal MOSFET. Once the MOSFET is turned on, the current is injected to AGND through the internal integrated resistor, where its resistance value is approximately  $3.7k\Omega$ . Figure 29 shows the recommended LED connection circuit.

Figure 29. Recommended LED connection circuit

The following table lists LED pin states which indicate various operating statuses and fault conditions of the MK3614T.

Table 2. LED pin functions

| LED Indication    | Status                        | Note                                                     |  |  |

|-------------------|-------------------------------|----------------------------------------------------------|--|--|

| LED on            | Port successfully powered at  | The MOSFET that controls the LED output is turned        |  |  |

| LED OII           | requested power level         | on.                                                      |  |  |

| LED off           | Looking for a valid detection | The MOSFET that controls the LED output is turned        |  |  |

| LED OII           | signature                     | off.                                                     |  |  |

| LED blinking only | Error condition, such as OCP, | The MOSFET that controls the LED output is               |  |  |

| several times     | ICUT, port short fault, OTP   | alternately switched on and off several times, then off. |  |  |

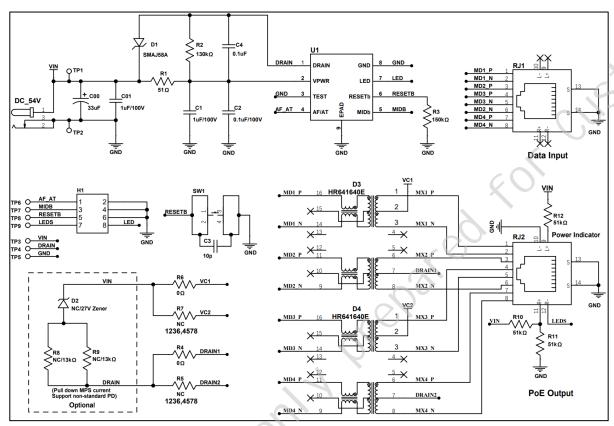

# 9. Application Examples

Figure 30. Application Schematic Example

# 10. Power Supply Recommendations

# 11. Layout

### 11.1 Layout Guidelines

To achieve high performance of the MK3614T, the following layout tips must be followed.

- At least one low-ESR ceramic bypass capacitor for the VPWR pin must be used. Place the capacitor as close as possible to the MK3614T VPWR pin.

- 2. The unidirectional TVS connected between VPWR and DRAIN must be employed to prevent an external lightning strike and surge current from damaging the chip.

- The recommended voltage of the LED pin is not higher than 30V and the current does not exceed 1mA, otherwise it may damage the pin. The pin voltage can be reduced by a pulldown resistor divider.

- 4. TEST pin is recommended to be tied to GND, and thermal pad is used for chip heat dissipation.

- 5. Use short, wide traces whenever possible for high power paths.

### 11.2 Layout Example

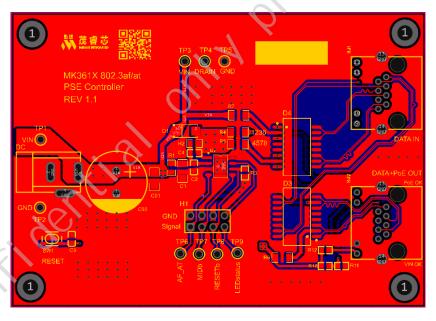

Figure 31. Evkit Layout (Tope Layer)

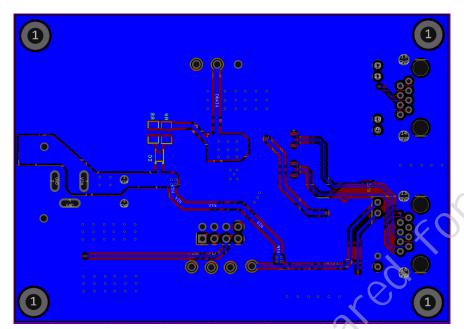

Figure 32. Evkit Layout (Bottom Layer)

# 12. Device and Documentation Support

- 12.1 Device Support

- 12.2 Documentation Support

- 12.3 Receiving Notification of Documentation Updates

- 12.4 Support Resources

- 12.5 Trademarks

### 12.6 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Meraki Integrated recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device to not meet its published specifications.

# 13. Mechanical, Packaging

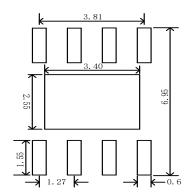

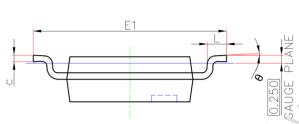

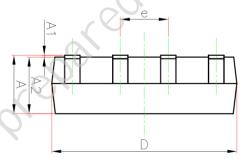

Figure 33. Recommended Land Pattern (mm)

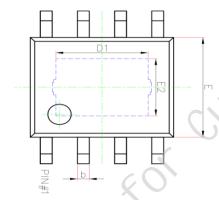

Figure 34. MK3614T Top View

Figure 35. MK3614T Side View

Figure 36. MK3614T Side View

|            | CVMDOL | Millin | neter |

|------------|--------|--------|-------|

|            | SYMBOL | MIN    | NOM   |

|            | Α      | 1.300  | 1.700 |

|            | A1     | 0.000  | 0.100 |

|            | A2     | 1.350  | 1.550 |

|            | b      | 0.330  | 0.510 |

|            | С      | 0.170  | 0.250 |

|            | D      | 4.700  | 5.100 |

|            | D1     | 3.050  | 3.250 |

| •          | Ш      | 3.800  | 4.000 |

|            | E1     | 5.800  | 6.200 |

|            | E2     | 2.160  | 2.360 |

| <b>(</b> 0 | е      | 1.270( | BSC)  |

|            | L      | 0.400  | 1.270 |

|            | θ      | 0°     | 8°    |

|            |        |        |       |

MK3614T v1.0 Specifications Subject to Change without notice www.meraki-ic.com

21

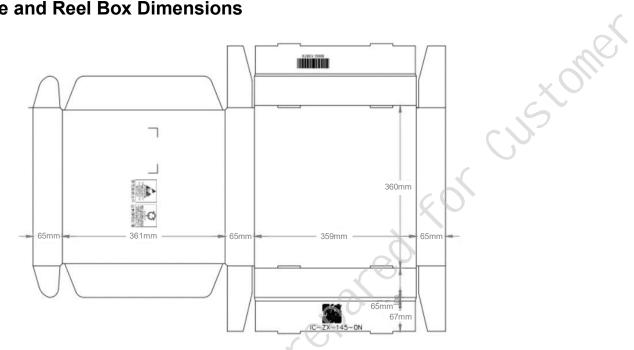

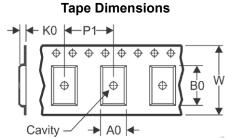

# 14. Reel and Tape Information

# **Reel Dimensions** Reel Diameter Reel Width(W1)

| Α0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

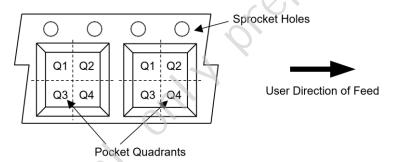

### **Quadrant Assignments For Pin 1 Orientation In Tape**

| Device  | Package<br>Type | Pins    | Quantities | Reel Diameter | Reel Width |

|---------|-----------------|---------|------------|---------------|------------|

|         |                 |         |            | (mm)          | W1(mm)     |

| MK3614T | ESOP8           | 8       | 4000       | 330           | 12.4       |

| A0 (mm) | B0 (mm)         | K0 (mm) | P1 (mm)    | W (mm)        | Pin1       |

|         |                 |         |            |               | Quadrant   |

| 6.4     | 5.4             | 2.1     | 8.0        | 12.0          | Q1         |

# 15. Tape and Reel Box Dimensions