Stome

## MK2552 Critical Conduction Mode PFC Controller

## 1. Description

The MK2552 families are critical conduction mode (CrM) power factor correction (PFC) controllers for high performance AC/DC power systems. With the highly linear multiplier and THD optimizer, the MK2552 can achieve ultralow THD and near unity power factor under different operation conditions. The MK2552 operates over a wide supply voltage range from 11V to 30V, which is suitable for a variety of application scenarios. Ultra-low startup current and optimized VCC undervoltage protection makes startup easier for selfpowered systems. In application scenarios that focus on light-load efficiency, the MK2552 can choose to enter the discontinuous conduction mode (DCM). In this mode, when the switching frequency exceeds frequency clamping threshold, the circuit operates in DCM with valley turn-on. The Intelligent protection functions and strategies of MK2552 can effectively reduce MOSFET electrical stress and greatly improve system reliability, such as soft-start and soft-stop protection, brown-in and brown-out protection, smart high/low line overcurrent protection, etc.

## 2. Applications

- AC/DC Adapters/Charger

- Industrial Power Supplies

- TV, Desktop PC, Monitor

- Lighting Application

## 3. Features

- Operates in a Wide VCC Voltage Range from 11V-30V

- Ultra-Low Quiescent Current: <160uA

- Ultra-Low Startup Current: <20uA

- Total Harmonic Compensator for AC Zero-Crossing

- Ultra-low THD & Unity Power Factor

- Smart High/Low Line Overcurrent Protection and Soft Start Function (MK2552, MK2552Q)

- Maximum Operating Frequency Limit and Valley Switching (MK2552Q)

- On-Chip Current Sense Filter

- Brown-In and Brown-Out Protection (MK2552, MK2552Q)

- Noise Immunity Enhancement

- Feedback Open Loop Protection (MK2552A, MK2552Q)

- Package: SOP-8

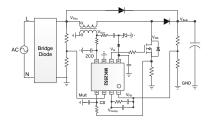

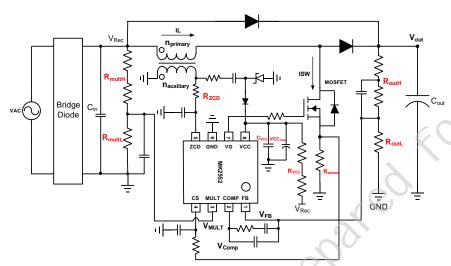

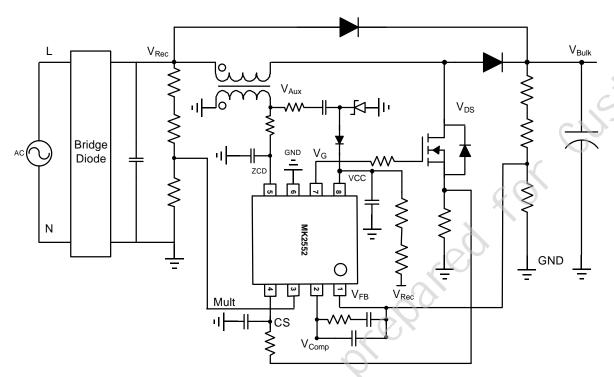

# 4. Typical Application

**Figure 1. Typical Application Diagram**

## 5. Order Information

| Order Part Number | Descriptions               |

|-------------------|----------------------------|

| MK2552XAB         | SOP-8, tape, 4000 pcs/reel |

| MK2552AXAB        | SOP-8, tape, 4000 pcs/reel |

| MK2552QXAB        | SOP-8, tape, 4000 pcs/reel |

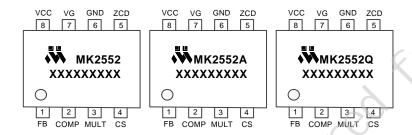

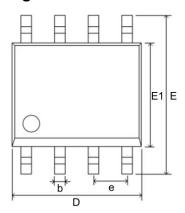

# 6. Pin Configuration and Functions

Figure 2. Pin Connection (top view)

Table 1. Pin Functions

|   |               | Pin                                                                                                                                                              | Descriptions                                                                                                                                                                                                                                                      |

|---|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ı | NO.           | Name                                                                                                                                                             | Descriptions                                                                                                                                                                                                                                                      |

|   | 1             | FB                                                                                                                                                               | Negative input of the error amplifier (E/A). The information on the output voltage of the PFC pre-regulator is fed into the pin through a resistor divider.                                                                                                       |

|   | 2             | COMP                                                                                                                                                             | Output of the error amplifier. A compensation network is placed between this pin and FB (pin#1) to achieve stability of the voltage control loop and ensure high power factor and low THD.                                                                        |

|   | 3             | Main input to the multiplier. This pin is connected to the rectified mains voltage via a resistor divider and provides sinusoidal reference to the current loop. |                                                                                                                                                                                                                                                                   |

|   | 4             | CS                                                                                                                                                               | Input to the PWM comparator. The current flowing in the MOSFET is sensed through a resistor, the resulting voltage is applied to this pin and compared with an internal sinusoidal-shaped reference, generated by the multiplier, to determine MOSFET's turn-off. |

|   | 5             | ZCD                                                                                                                                                              | Boost inductor's demagnetization sensing input for transition-mode operation. A negative-going edge triggers MOSFET's turn-on.                                                                                                                                    |

|   | 6             | GND                                                                                                                                                              | Ground. Current return for both the signal part of the IC and the gate driver.                                                                                                                                                                                    |

|   | $\mathcal{C}$ | VG                                                                                                                                                               | Gate driver output.                                                                                                                                                                                                                                               |

|   | 8             | VCC                                                                                                                                                              | Supply Voltage of both the signal part of the IC and the gate driver.                                                                                                                                                                                             |

## 7. Specifications

## 7.1 Absolute Maximum Ratings (1)

| Symbol                 | Parameter                         | Min  | Max | Unit |

|------------------------|-----------------------------------|------|-----|------|

| VCC                    | supply voltage VCC                | -0.3 | 32  | ×    |

| FB, COMP, MULT, CS (2) | -0.3                              | 8    | V   |      |

| VG <sup>(2)</sup>      | voltage on pin VG                 | -0.3 | 14  |      |

| $T_J$                  | operating junction temperature,   | -40  | 150 |      |

| T <sub>stg</sub>       | storage temperature               | -55  | 150 | °C   |

| $T_{sld}$              | soldering temperature (10 second) |      | 260 |      |

### Notes:

- (1) Stresses beyond the "ABSOLUTE MAXIMUM RATINGS" may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated in "RECOMMENED OPERATING CONDITIONS". Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- (2) Output pin not to be voltage driven.

## 7.2 ESD Ratings

|                            |                                                                               | Value | Unit     |

|----------------------------|-------------------------------------------------------------------------------|-------|----------|

| Electrostatic              | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>   | ±2500 | <b>V</b> |

| discharge V <sub>ESD</sub> | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | ±2000 | V        |

### Notes:

- JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

- JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

| . 6                  |                                                   | Min  | Max | Unit |

|----------------------|---------------------------------------------------|------|-----|------|

| Recommended          | VCC supply voltage                                | 12   | 28  | V    |

| Operation Conditions | ZCD max current                                   | -0.8 | 0.8 | mA   |

| operation contained  | operating junction temperature. (T <sub>J</sub> ) | -40  | 125 | °C   |

## 7.4 Thermal Information

|                                              |                                        |                                    | Value | Unit |  |  |  |  |  |

|----------------------------------------------|----------------------------------------|------------------------------------|-------|------|--|--|--|--|--|

| Package Thermal<br>Resistance <sup>(1)</sup> |                                        | $	heta_{JA}$ (Junction to ambient) |       | °C/W |  |  |  |  |  |

|                                              |                                        | $\theta_{JC}$ (Junction to case)   | 75    | ]    |  |  |  |  |  |

| Note:                                        |                                        |                                    |       |      |  |  |  |  |  |

| (1) Measu                                    | (1) Measured on JESD51-7, 4-layer PCB. |                                    |       |      |  |  |  |  |  |

### 7.5 Electrical Characteristics

$-40^{\circ}\text{C} \le T_{A} = T_{J} \le 125^{\circ}\text{C}$ .  $V_{CC} = 13V_{DC}$ ,  $1\mu\text{F}$  from VCC to GND. All voltages are measured with respect to ground (pin 6). Currents are positive when flowing into the IC, unless otherwise specified.

|                          | Parameter                                  | Test Conditions                                                                                                                              | Min        | Тур          | Max        | Unit |

|--------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|------------|------|

| Supply Curre             | nt                                         |                                                                                                                                              |            |              | •          |      |

| I <sub>st</sub>          | Start-up current                           | Before turn-on,<br>Vcc=11V                                                                                                                   |            | 20           | 35         | μА   |

| Iq                       | Quiescent current                          | V <sub>CC</sub> =13V, V <sub>FB</sub> =3V                                                                                                    |            | 160          | 230        | μA   |

| l <sub>op</sub>          | Operating supply current                   | T <sub>J</sub> =+25°C;<br>F <sub>sw</sub> =70kHz,<br>C <sub>load</sub> =1nF at VG<br>F <sub>sw</sub> =70kHz,<br>C <sub>load</sub> =1nF at VG |            | 1.3          | 1.8        | mA   |

| Supply Voltage           | je                                         | Oload=1111 at VO                                                                                                                             |            | 00           | ı          |      |

| Vcc                      | Operating range                            | After turn-on                                                                                                                                | 11         | <del>\</del> | 30         | V    |

| Vcc_on                   | Turn-on threshold                          | 11                                                                                                                                           |            | 12           | 13         | V    |

| Vcc_off                  | Turn-off threshold                         |                                                                                                                                              | 8.7        | 9.5          | 10.5       | V    |

| V <sub>CC_Hys</sub>      | Threshold hysteresis                       | T <sub>J</sub> =+25°C<br>T <sub>J</sub> =-40~+125°C                                                                                          | 2.1<br>1.7 |              | 2.6<br>3.2 | ٧    |

| Vz                       | VCC holding threshold                      | I <sub>CC</sub> =20mA                                                                                                                        | 30         | 32           | 35         | V    |

| Multiplier Inpu          | ut                                         |                                                                                                                                              | '          |              | •          |      |

| I <sub>mult</sub>        | Input bias current (1)                     | V <sub>mult</sub> =2V                                                                                                                        |            |              | 1          | μΑ   |

| V <sub>mult</sub>        | Linear operating range                     |                                                                                                                                              | 0 to 3     |              |            | V    |

| ΔVcs /ΔV <sub>mult</sub> | Output max slope (1)<br>(MK2552)           | V <sub>COMP</sub> =upper clamp,                                                                                                              |            | 2            |            | V/V  |

|                          | Output max slope (1)<br>(MK2552A, MK2552Q) | V <sub>mult</sub> =0V to 0.9V                                                                                                                |            | 1.3          |            | V/V  |

| K                        | Multiplier output gain (MK2552)            | V <sub>mult</sub> =1V,<br>V <sub>COMP</sub> =4V;<br>T <sub>J</sub> =+25°C                                                                    | 0.50       | 0.60         | 0.77       | 1/V  |

| IX.                      | Multiplier output gain (MK2552A, MK2552Q)  | V <sub>mult</sub> =2.2V,<br>V <sub>COMP</sub> =3V;<br>T <sub>J</sub> =+25°C                                                                  | 0.13       | 0.23         | 0.33       | 1/V  |

| Error Amplifie           | er                                         |                                                                                                                                              |            |              |            |      |

| $V_{FB}$                 | Feedback voltage                           | T <sub>J</sub> =+25°C                                                                                                                        | 2.455      | 2.510        | 2.575      | V    |

| VFB                      | threshold                                  | T <sub>J</sub> =-40~+125°C                                                                                                                   | 2.42       | 2.51         | 2.59       | v    |

| I <sub>FB</sub>          | Input bias current (1)                     | V <sub>FB</sub> =2.5V                                                                                                                        |            |              | 1          | μΑ   |

| I <sub>COMP</sub>        | Source current (1)                         | V <sub>COMP</sub> =4V, V <sub>FB</sub><br>=2.4V                                                                                              |            | -3.6         |            | mA   |

| ICOMP                    | Sink current (1)                           | V <sub>COMP</sub> =4V, V <sub>FB</sub><br>=2.6V                                                                                              |            | 5.7          |            | mA   |

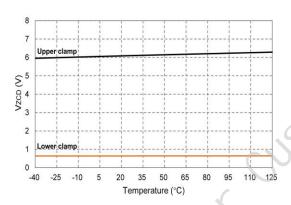

| V                        | Upper clamp voltage                        | I <sub>source</sub> =0.5mA,<br>V <sub>CC</sub> =13V, T <sub>J</sub> =+25°C                                                                   | 5.4        | 5.9          | 6.5        | V    |

| V <sub>COMP</sub>        | Lower clamp voltage                        | I <sub>sink</sub> =0.1mA,<br>V <sub>CC</sub> =13V, T <sub>J</sub> =+25°C                                                                     | 2          | 2.15         | 2.3        | ٧    |

| V <sub>FB_dis</sub>      | FB Disable threshold (MK2552A, MK2552Q)    |                                                                                                                                              | 260        | 300          | 340        | mV   |

| V <sub>FB_en</sub>              | FB Enable threshold                                                    |                                                   | 360  | 400  | 440  | mV |

|---------------------------------|------------------------------------------------------------------------|---------------------------------------------------|------|------|------|----|

| Brown-In Brown<br>(MK2552, MK25 | │ (MK2552A, MK2552Q)<br>n-Out Protection and Line<br>52Q)              | Feed Forward                                      |      |      |      |    |

| V <sub>BI</sub>                 | Brown-in Threshold                                                     |                                                   | 0.8  | 0.9  | 1    | V  |

| V <sub>BO</sub>                 | Brown-out Threshold                                                    |                                                   | 0.7  | 0.8  | 0.9  | V  |

| VHL                             | Comparator threshold for high line detection                           |                                                   | 1.9  | 2    | 2.1  | V  |

| VLL                             | Comparator threshold for low line detection                            |                                                   | 1.6  | 1.7  | 1.8  | V  |

| Output Overvol                  | tage                                                                   |                                                   |      |      |      |    |

|                                 | Dynamic OVP<br>triggering current<br>(MK2552)                          | T <sub>J</sub> =+25°C                             | 33   | 38   | 43   | μА |

| lovp                            | Dynamic OVP<br>triggering current<br>(MK2552A, MK2552Q)                | T <sub>J</sub> =+25°C                             | 23.5 | 27.0 | 30.5 | μA |

| lovp_Hys                        | Dynamic OVP current<br>hysteresis <sup>(1)</sup><br>(MK2552)           |                                                   |      | 20   |      | μА |

| TOVP_mys                        | Dynamic OVP current<br>hysteresis <sup>(1)</sup><br>(MK2552A, MK2552Q) | ~                                                 | 87   | 10   |      | μA |

| V <sub>OVP</sub>                | Static OVP threshold                                                   | , 9                                               | 2    | 2.15 | 2.3  | V  |

| Current Sense                   | Comparator                                                             |                                                   |      |      |      |    |

| Ics                             | Input bias current (1)                                                 | V <sub>CS</sub> =1V                               |      |      | 1    | μΑ |

| T <sub>dly</sub>                | Delay to output (1)                                                    | 0),                                               |      | 100  |      | ns |

| Vcs_offset                      | Current sense offset (1)                                               | V <sub>mult</sub> =0V                             |      | 30   |      | mV |

|                                 | ×                                                                      | V <sub>mult</sub> =3V                             |      | 0    |      |    |

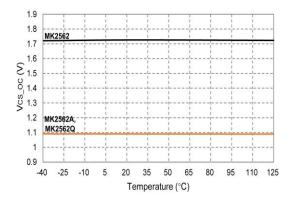

|                                 | OC threshold (MK2552)                                                  | .,                                                | 1.6  | 1.7  | 1.8  | V  |

| Vcs_oc                          | OC threshold<br>(MK2552A, MK2552Q)                                     | V <sub>COMP</sub> =upper clamp                    | 1    | 1.1  | 1.2  | V  |

| v (*)                           | OC threshold when low<br>line is detected<br>(MK2552)                  | V                                                 | 1.6  | 1.7  | 1.8  | V  |

| Vcs_oc_ll                       | OC threshold when low<br>line is detected<br>(MK2552Q)                 | V <sub>сомР</sub> =upper clamp                    | 1    | 1.1  | 1.2  | V  |

| V                               | OC threshold when high line is detected (MK2552)                       | V upper alone                                     | 1    | 1.1  | 1.2  | V  |

| Vcs_oc_hl                       | OC threshold when high line is detected (MK2552Q)                      | V <sub>COMP</sub> =upper clamp                    | 0.6  | 0.7  | 0.8  | V  |

| Zero Current De                 | etector                                                                |                                                   |      |      |      |    |

| V <sub>ZCDH</sub>               | Upper clamp voltage                                                    | I <sub>ZCD</sub> =0.5mA,<br>T <sub>J</sub> =+25°C | 5.5  | 5.7  | 6.6  | V  |

| Vzcdl                | Lower clamp voltage                                  | I <sub>ZCD</sub> =-0.5mA,<br>T <sub>J</sub> =+25°C | 0.5 | 0.65 | 0.8 | V   |

|----------------------|------------------------------------------------------|----------------------------------------------------|-----|------|-----|-----|

| Vzcda                | Arming voltage<br>(MK2552)                           |                                                    | 2   | 2.1  | 2.2 | V   |

| V ZCDA               | Arming voltage<br>(MK2552A, MK2552Q)                 |                                                    | 1.3 | 1.4  | 1.5 | V   |

| Vzcot                | Triggering voltage (MK2552)                          |                                                    | 1.5 | 1.6  | 1.7 | V   |

| V ZCDI               | Triggering voltage (MK2552A, MK2552Q)                |                                                    | 0.6 | 0.7  | 0.8 | V   |

| I <sub>ZCD</sub>     | Input bias current (1)                               | Vzcd=3V                                            |     |      | 1   | μA  |

| I <sub>ZCD_src</sub> | Source current (1)                                   | V <sub>CC</sub> =13V,<br>V <sub>ZCD</sub> =0.3V    |     | -4.5 |     | mA  |

| IzcD_snk             | Sink current (1)                                     | V <sub>CC</sub> =13V,<br>V <sub>ZCD</sub> =6.3V    |     | 1    |     | mA  |

| $V_{ZCD\_dis}$       | ZCD Disable threshold                                |                                                    | 260 | 300  | 340 | mV  |

| V <sub>ZCD_en</sub>  | ZCD Enable threshold                                 |                                                    | 360 | 400  | 440 | mV  |

| Gate Driver          |                                                      |                                                    |     |      |     |     |

| V <sub>L</sub>       | Gate low level (1)                                   | I <sub>gate</sub> =200mA                           | 700 |      | 1   | V   |

| V <sub>H</sub>       | Gate high level                                      | I <sub>gate</sub> =200mA                           | 10  |      | 13  | V   |

| V <sub>clamp</sub>   | Gate clamp voltage                                   | Vcc=28V                                            | 11  | 12.5 | 14  | V   |

| Tr                   | Gate rising time (1) (20%~80%)                       | C <sub>load</sub> =1nF,                            |     | 28   |     | ns  |

| $T_f$                | Gate falling time <sup>(1)</sup> (80%~20%)           | C <sub>load</sub> =1nF                             |     | 13   |     | ns  |

| Starter              |                                                      |                                                    |     |      |     |     |

| T <sub>start</sub>   | Start timer period                                   |                                                    | 100 | 190  | 230 | μs  |

| Tss                  | Soft start time<br>(MK2552, MK2552Q)                 |                                                    | 5   | 10   | 15  | ms  |

| Maximum O            | perating Frequency Limit                             |                                                    |     |      |     |     |

| F <sub>sw_max</sub>  | Maximum switching frequency <sup>(1)</sup> (MK2552Q) |                                                    |     | 135  |     | kHz |

### Note:

Values are guaranteed by design and verified by characterization on bench, not tested in production.

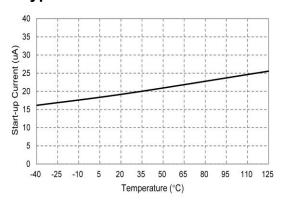

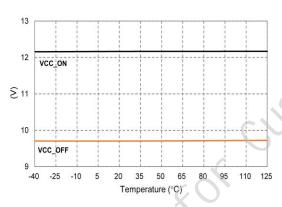

## 7.6 Typical Characteristics

Figure 3. Start-up Current vs Temperature

Figure 4. Start-up & UVLO vs Temperature

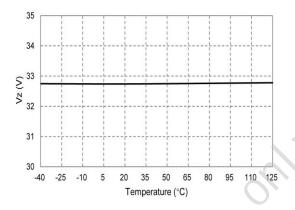

Figure 5. VCC Zener Voltage vs Temperature

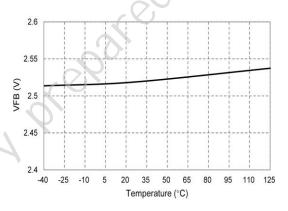

Figure 6. Feedback Reference vs **Temperature**

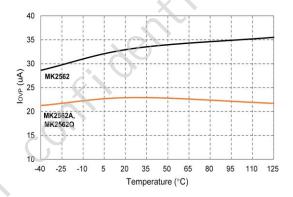

Figure 7. OVP Current vs Temperature

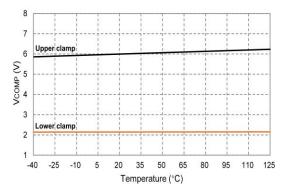

Figure 8. E/A Output Clamp Levels vs **Temperature**

Figure 9. VCS Clamp vs Temperature

Figure 10. ZCD Clamp Levels vs **Temperature**

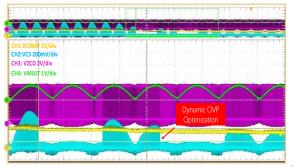

Figure 11. Dynamic OVP Test

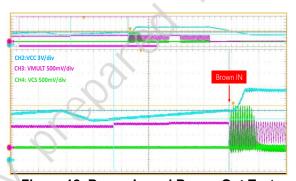

Figure 12. Brown In and Brown Out Test

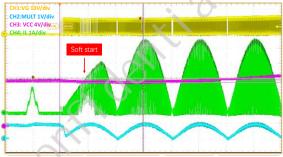

Figure 13. System Soft Startup Test

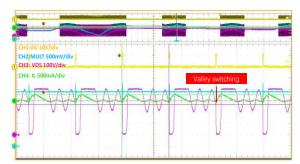

Figure 14. Frequency Limit and Valley **Switching Test**

## 8. Detailed Description

### 8.1 Overview

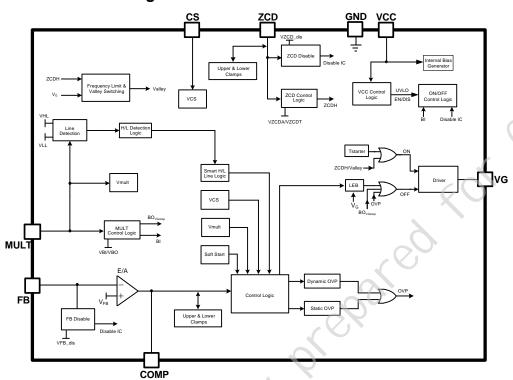

The MK2552 families are critical conduction mode (CrM) power factor correction (PFC) controllers for high performance AC/DC power systems, which achieve ultra-low THD and near unity power factor under different operation conditions. It features an operational amplifier for feedback error processing, a highly linear multiplier for low THD, a current-sense comparator, a current zero-crossing detector, PWM logic, and a driver for external FET, etc.

The MK2552 is pin compatible with other industrial controllers providing similar functions, while richer enhancement features have been implemented to reduce bill of materials (BOM) cost. The system performance is enhanced by increasing the operating voltage range and optimizing the startup strategy, which makes the controller easier to start in the self-powered system. The device also features an innovative dynamic overvoltage protection enhancement circuit, which improves the performance of the system under dynamic load. The soft start function and optimized operating currents of the device result in low current stress and low power consumption. The Intelligent protection functions and strategies of MK2552 can greatly improve system reliability, such as feedback open loop protection, soft stop protection, brown in/brown out protection, and smart high/low line overcurrent protection.

MK2552 includes a range of features designed to make the PFC converter operation well controlled and protected. It can be flexibly configured according to requirements. MK2552Q includes frequency limit and valley switching functions. In application scenarios that focus on light-load efficiency, MK2552Q enters the discontinuous conduction mode (DCM). In this mode, when the switching frequency exceeds the frequency clamping threshold, the circuit operates in DCM with valley turn-on. MK2552, MK2552A, and MK2552Q can be selected according to usage requirements. Table 2 compares the three devices, those parameters that may result in different values of the external components.

Table 2. MK2552A and MK2552Q vs MK2552

| Parameter                                   | MK2552    | MK2552A   | MK2552Q |  |  |

|---------------------------------------------|-----------|-----------|---------|--|--|

| H/L line overcurrent protection             | Yes       | No        | Yes     |  |  |

| FB disable function                         | No        | Yes       | Yes     |  |  |

| Soft start function                         | Yes       | No        | Yes     |  |  |

| Brown-out protection and soft stop function | Yes       | No        | Yes     |  |  |

| Frequency limit and valley switching        | No        | No        | Yes     |  |  |

| Multiplier gain (typ.)                      | 0.6       | 0         | .42     |  |  |

| Current sense reference clamp (typ.)        | 1.7 V     | 1.        | 1 V     |  |  |

| Dynamic OVP triggering current (typ.)       | 33 uA     | 23 uA     |         |  |  |

| ZCD arm/trigger thresholds (typ.)           | 2.1/1.6 V | 1.4/0.7 V |         |  |  |

## 8.2 Functional Block Diagram

Figure 15. Block Diagram

### 8.3 Feature Description

### 8.3.1 VCC Power Supply and Undervoltage Lockout

The MK2552 operates from a supply voltage of 11V to 30V. This feature makes MK2552 suitable for a variety of application scenarios. For the best performance, use a typical 0.1uF decoupling capacitor as close as possible between the VCC and GND pins of MK2552. A VCC bypass capacitor (1uF to 10uF) in parallel to the decoupling capacitor is also recommended to reduce noise ripple during switching.

MK2552 has an internal undervoltage lockout (UVLO) protection feature in the VCC supply circuit blocks. When the voltage on the VCC pin exceeds  $V_{\text{CC-ON}}$ , the controller leaves the UVLO state and activates the circuitry. When VCC voltage drops to below  $V_{\text{CC-OFF}}$ , the controller re-enters the UVLO state.

### 8.3.2 Disable Function

When FB pin voltage is below  $V_{FB\_dis}$ , it shuts down the MK2552 and reduces its consumption at a lower value. To restart the IC, the FB pin voltage must exceed  $V_{FB\_en}$ . Using this function, the user can flexibly control the operating state of the MK2552.

However, it also provides a certain degree of additional security. When the lower resistor of the output voltage divider is shorted to ground or the upper resistor is missing, the MK2552 will be in the off-protection state. The MK2552 ZCD pin also has similar functions.

### 8.3.3 Soft Start Function

During startup, the output capacitor voltage has not yet been established. When the converter is started or the converter is started with load, it will bring greater current stress to the MOSFET, reducing the reliability of the system. The MK2552 adds a soft start feature to prevent this. In the start-up stage (T<sub>SS</sub>), the soft start function is achieved by linearly raising the overcurrent protection threshold, so that the conduction current on the MOSFET rises steadily.

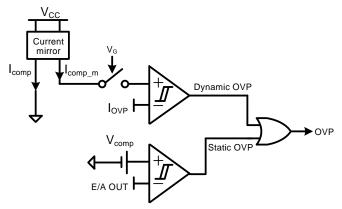

## 8.3.4 Output Overvoltage Function

When the output voltage is higher than the set overvoltage protection point, the difference current will flow through the compensation network and enter the error amplifier output (pin COMP). This current is monitored inside the device. As the current exceeds I<sub>OVP</sub>, the OVP is triggered (Dynamic OVP).

When the load of the PFC converter is very low, the output voltage tends to stay steadily above the nominal value, which cannot be handled by the Dynamic OVP. If this occurs, however, the error amplifier output will saturate low. When this is detected, the external power transistor is switched off and the MK2552 is put in an idle state (Static OVP).

When the system performs a load jump, the MK2552 also adds dynamic overvoltage protection enhancement optimization, which can make the drive waveform as continuous as possible. This improves system noise and ripple. The control diagram is shown on Figure 16.

Figure 16. Overvoltage Function Logic Control Diagram

### 8.3.5 Overcurrent Protection

Under certain conditions, (such as inrush, brown-out recovery, and output over-load) the PFC power stage will see large currents. It is critical that the power devices be protected from switching during these conditions.

A shunt resistor in series with the MOSFET source leg is used to sense the peak currents. When the MOSFET is turned on, the conduction current flows through the detection resistor. When the voltage at the resistor is higher than  $V_{CS\_OC}$ , the MOSFET is turned off, the MK2552 triggers overcurrent protection.

The reference voltage for overcurrent detection in traditional controllers is always a fixed value. However, when the system input voltage changes and the detection resistance is fixed, it can lead to changes in the actual overcurrent protection threshold. Consequently, under high input voltage, MOSFETs may be damaged due to the overcurrent protection threshold having not yet been reached.

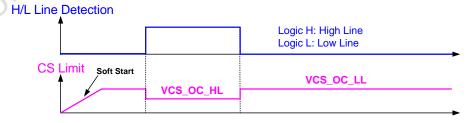

MK2552 has improved the above issues by designing a two-level overcurrent protection threshold based on the input voltage. When the voltage of the MULT pin is lower than  $V_{LL}$ , MK2552 determines that it is low line, and the overcurrent protection threshold,  $V_{CS\_OC\_LL}$  is used. When the voltage of the MULT pin is higher than  $V_{HL}$ , it is judged as high line and the overcurrent protection threshold is reduced to  $V_{CS\_OC\_HL}$ . In this way, the MK2552 can effectively solve the problem of high/low line overcurrent protection differences under wide input voltage conditions. The control diagram is shown on Figure 17.

Figure 17. High/Low Line Overcurrent Protection Control Diagram

13

#### 8.3.6 **Brownout Protection and Soft Stop Function**

As the power line voltage decreases, the input current must increase to maintain a constant output voltage for any specific load. Brownout protection helps prevent excess system thermal stress (due to the higher RMS input current) from exceeding a safe operating level.

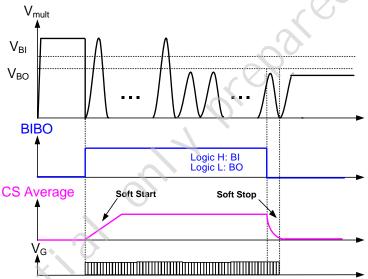

Power-line voltage is sensed at the MULT pin. When the MULT pin voltage fails to exceed the brown-out threshold (V<sub>BO</sub>), a brown-out condition is detected, and gate driver output does not immediately turn off until the input voltage approaches the trough. The addition of the soft stop function ensures a smooth shutdown and does not lead to incorrect startup due to oscillations. During brown-out, the COMP pin voltage is actively pulled low, soft-start condition is initiated and the VCC pin continues to sink about 1mA of current until the VCC voltage drops to UVLO. When

the MULT pin voltage rises above the brown in threshold (V<sub>BI</sub>) and the VCC pin exceeds V<sub>CC-ON</sub>, the power stage soft starts as COMP rises with controlled voltage. The control diagram is shown on Figure 18.  $V_{\text{mult}}$

Figure 18. Brownout Protection and Soft Stop Function Control Diagram

#### 8.3.7 Maximum Operating Frequency Limit and Valley Switching

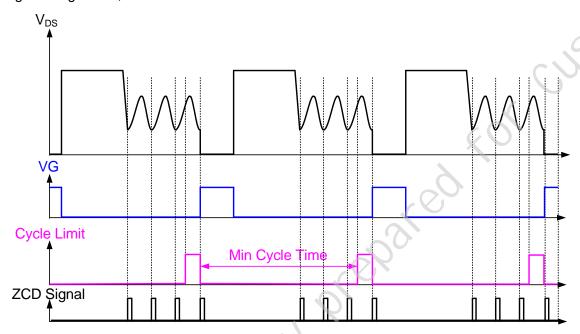

In application scenarios that focus on light-load efficiency, the high switching frequency of CrM increases system switching losses. This loss is difficult to ignore because the system itself is at an extremely light-load stage. Traditional controllers only have a frequency limiting function. Although the switching frequency is reduced, at the moment, the VDS voltage is still a high level. Then, the MOSFET is turned on, which increases switching loss and reduces system efficiency. The MK2552 can optionally add frequency limiting and valley switching functions.

Due to the addition of the frequency limiting function, the converter will enter the discontinuous conduction mode (DCM). In this mode, when the switching frequency exceeds the frequency clamping threshold, the circuit operates in DCM with valley turn-on. The control diagram is shown on Figure 19. As can be seen in the figure, the system has entered DCM due to a minimum cycle

MK2552 v0.8 www.meraki-ic.com Specifications Subject to Change without notice © 2024 Meraki IC. Confidential. Classified: Authorized Customer Only

time  $(1/F_{sw\_max})$ . The driver will turn on the MOSFET if the minimum cycle time is exceeded and the VDS is detected to be in a trough.

The addition of this function can significantly improve the efficiency of the system under high voltage and light load, but PF and THD will be affected to a certain extent.

Figure 19. Frequency Limit and Valley Switching Logic Control Diagram

# 9. Application and Implementation

## 9.1 Typical Applications

Figure 20. MK2552 Reference Design Circuit

### 9.2 Design Procedure

### 9.2.1 Supply Voltage

The supply voltage applied to the controller VCC pin should never exceed the absolute maximum ratings. Higher supply voltages require the consideration of chip power dissipation and junction temperature. In some scenarios where the supply voltage is high (for example, supply voltage greater than 30V), a high voltage LDO must be used so that the VCC pin does not exceed the absolute maximum ratings and reduce the power dissipation of the internal LDO.

MK2552 reference design circuit is shown in Figure 20. At startup, the MK2552 is powered by the VCC capacitor (VCC<sub>cap</sub>) that is charged via the resistors  $R_{VCC}$ . Connect a low-ESR ceramic decoupling capacitor ( $C_{VCC}$ ) between 100 nF and 1  $\mu$ F from VCC to GND for stability. The choice of capacitor voltage rating should also depend on the VCC voltage. Place the decoupling capacitor ( $C_{VCC}$ ) as close as possible to the MK2552 VCC and GND pins.

### 9.2.2 Zero Current Detector

The ZCD pin is the input for demagnetization induction of the boost inductor. In transition mode PFC, the ZCD pin is connected to the auxiliary winding of the boost inductor through a limiting resistor. Before triggering the ZCD circuit, the voltage on the ZCD pin must experience a positive-going edge exceeding  $V_{ZCDA}$  (due to the MOSFET's turnoff). When the voltage on the pin falls below  $V_{ZCDT}$ , it sets the PWM latch and the MOSFET is turned on. Therefore, the maximum main-to-auxiliary winding turn ratio,  $n_{max}$ , has to ensure that the voltage delivered to the pin during the MOSFET's OFF-time is sufficient enough to arm the ZCD circuit. A safe margin of 15% is added.

$$n_{max} = \frac{n_{primary}}{n_{auxiliary}} = \frac{V_{out} - \sqrt{2} * VAC_{max}}{1.15 * V_{ZCDA}}$$

The minimum value of the limiting resistor can be found considering the maximum voltage across the auxiliary winding and assumes a 0.8 mA current through the pin. During the MOSFET ON and OFF stages, two resistance values can be calculated.

$$R_1 = \frac{\frac{V_{out}}{n_{aux}} - V_{ZCDH}}{0.8mA}$$

$$R_2 = \frac{\frac{\sqrt{2} * VAC_{max}}{n_{aux}} - V_{ZCDL}}{0.8mA}$$

Out of the two values, the higher value between the two is limiting resistor.

$$R_{ZCD} = \text{Max}(R_1, R_2)$$

### 9.2.3 Overcurrent Protection

The CS pin is the inverting input of the current sense comparator. Through this pin, the MK2552 senses the instantaneous inductor current, which is converted to a proportional voltage by an external sense resistor (R<sub>sense</sub>). As this signal crosses the overcurrent threshold, the PWM latch is reset and the power MOSFET is turned off. The MOSFET stays in OFF-state until the PWM latch is reset by the ZCD signal.

The sense resistor value (R<sub>sense</sub>) can be calculated as follows.

$$R_{sense} < \frac{V_{CS\_OC\_min}}{IL_{pk}}$$

where,  $IL_{pk}$  is the maximum peak current in the inductor.  $V_{CS\_OC\_min}$  is the minimum voltage allowed on the MK2552 current sense. And then, based on the RMS switch current  $ISW_{rms}$ , the power dissipated in  $R_{sense}$  is given by:

$$P_{sense} = ISW_{rms}^{2} * R_{Sense}$$

### 9.2.4 Multiplier and Brownout Protection

The internal multiplier has two inputs, one from the instantaneous line voltage after rectification (MULT pin) and the other from the output of the error amplifier (COMP pin). The multiplier output is then fed into the PWM comparator and compared with the current sensing voltage VCS, to turn off the power MOSFET. The MK2552, which uses a multiplier, can directly follow the input current with the input voltage, achieving good power factor. The multiplier output can be described by the relationship:

$$V_{mult\_out} = K * (V_{COMP} - 2.5V) * V_{MULT}$$

where, the K is the multiplier gain,  $V_{COMP}$  is the voltage on COMP pin, and  $V_{MULT}$  is the voltage on MULT pin.

The linear operation of the multiplier is guaranteed within the range 0V to 3 V of  $V_{MULT}$ , and according to 9.3.6, the functional characteristics of brownout protection have been explained. If using the MK2552 with brownout protection, the  $V_{MULT}$  voltage at startup needs to be calculated first.

$$\frac{R_{multL} * \sqrt{2} * VAC_{min}}{R_{multL} + R_{multH}} > V_{BI}$$

Below is supposing a 200 µA current flowing into the multiplier divider. Please note that for R<sub>multH</sub> a resistor with a suitable voltage rating is needed, or more resistors in series must be used.

$$R_{multH} = \frac{\sqrt{2} * VAC_{max}}{200 \, \mu A}$$

### 9.2.5 Output Overvoltage Protection

According to 9.3.4, the functional characteristics of output overvoltage protection have been explained. The voltage at FB pin will be kept at  $V_{FB}$  by the local feedback of the error amplifier. The network connected between FB and COMP introduces a time constant to achieve high PF. If there is any abrupt change of output voltage, the MK2552 monitors the current flowing into the error amplifier output pin. When the detected current is higher than  $I_{OVP}$ , the dynamic OVP is triggered, the MK2552 will be disabled, and the driver signal will be stopped. Therefore, the  $R_{outH}$  and  $R_{outL}$  are then selected as follows:

$$R_{outH} = \frac{\Delta V_{OVP}}{I_{OVP}}$$

where, the  $\Delta V_{OVP}$  is the difference between the maximum allowable overvoltage and the output voltage.

$$R_{outL} = \frac{V_{FB} * R_{outH}}{V_{out} - V_{FB}}$$

Please note that for R<sub>outH</sub> a resistor with a suitable voltage rating is needed, or more resistors in series must be used.

## 10. Power Supply Recommendations

## 11. Layout

#### 11.1 **Layout Guidelines**

To achieve high performance of the MK2552, the following layout tips must be followed:

- Use separate clean traces for VCC and GND pins.

- At least one low-ESR ceramic bypass capacitor(100nF) must be used. Place the capacitor as close as possible to the MK2552 VCC and GND pins.

- The GND pin on the ground plane needs to route with a short and wide trace. It is necessary to note that the power GND and signal GND should be routed separately, and a single point of ground should be maintained.

- In order to minimize interference caused by capacitive coupling of the boost inductor, the device should maintain a distance from the boost inductor. It is also recommended that the device not be placed underneath magnetic elements.

- Because of the precise zero current detection requirement, the ZCD resistor should be placed as close as possible to the ZCD pin.

- 6. Keep the loop area between the CS sampling resistor and the CS pin as small as possible.

- Avoid placing the FB, COMP and MULT traces close to any other high dV/dT traces that would induce significant noise into the high impedance leads.

- The trace from the VG pin to the gate of the MOSFET needs to be as short as possible. 8.

- When VDS capacitors have to be added to solve EMC problems, it should be as close to the MOSFET as possible. Preventing VG pin oscillation.

www.meraki-ic.com © 2024 Meraki IC. Confidential. Classified: Authorized Customer Only

Chexoluex

## 11.2 Layout Example

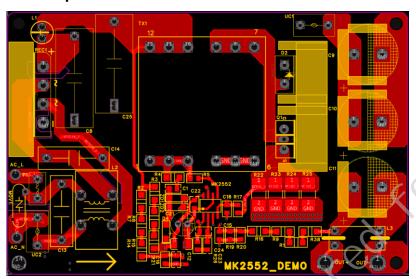

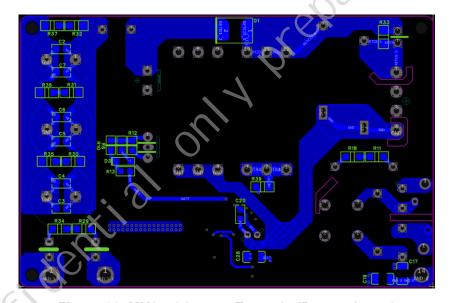

Figure 21. MK2552 Layout Example (Top Layer)

Figure 22. MK2552 Layout Example (Bottom Layer)

www.meraki-ic.com © 2024 Meraki IC.

Figure 23. MK2552 Typical Schematic

Meraki conflidential

## 12. Device and Documentation Support

- 12.1 **Device Support**

- 12.2 **Documentation Support**

- 12.3 **Receiving Notification of Documentation Updates**

- 12.4 **Support Resources**

- 12.5 **Trademarks**

#### 12.6 **Electrostatic Discharge Caution**

This integrated circuit can be damaged by ESD. Meraki Integrated recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

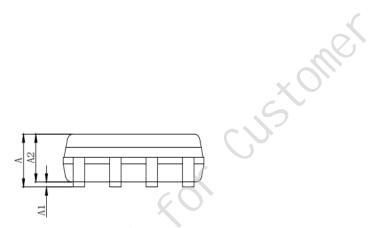

# 13. Mechanical, Packaging

## 13.1 Package Size

Figure 24. SOP-8 Top View

Figure 25. SOP-8 Side View

Figure 26. SOP-8 Side View

| SYMBOL   | Dimensions In Millimeters |        |  |  |  |

|----------|---------------------------|--------|--|--|--|

| OTIVIDOL | MIN                       | MAX    |  |  |  |

| A        | 1.30                      | 1.75   |  |  |  |

| A1       | 0.05                      | 0.25   |  |  |  |

| A2       | 1.25                      | 1.65   |  |  |  |

| b        | 0.33                      | 0.51   |  |  |  |

| С        | 0.20                      | 0.25   |  |  |  |

| D        | 4.7                       | 5.1    |  |  |  |

| Е        | 5.8                       | 6.2    |  |  |  |

| E1       | 3.8                       | 4.0    |  |  |  |

| е        | 1.27                      | 0(BSC) |  |  |  |

| L        | 0.40                      | 1.27   |  |  |  |

| θ        | 0°                        | 8°     |  |  |  |

### Note:

(1) This drawing is subject to change without notice

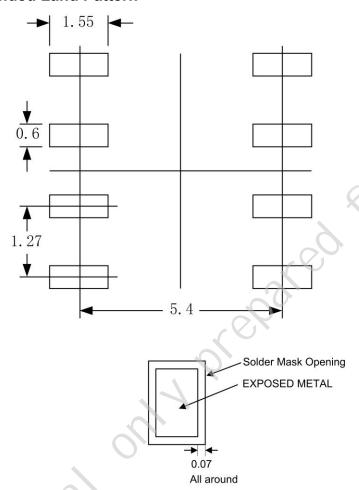

#### 13.2 **Recommended Land Pattern**

Figure 27. Recommended Land Pattern

Notes: (continued)

- (1) All linear dimensions are in millimeters.

- (2) It is recommended that vias under paste be filled, plugged or tented.

MK2552 v0.8 www.meraki-ic.com © 2024 Meraki IC. Confidential. Classified: Authorized Customer Only

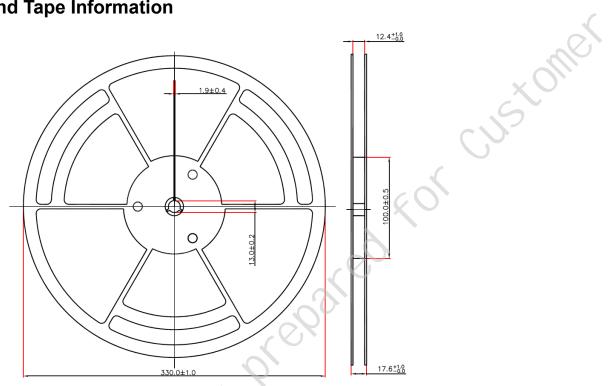

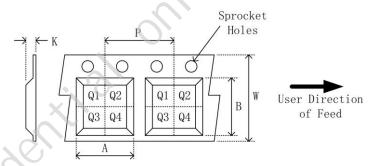

# 14. Reel and Tape Information

Figure 28. Reel Dimensions

| Device     | Package | Pins | SPQ   | Α             | В       | K       | Р     | W      | Pin1     |

|------------|---------|------|-------|---------------|---------|---------|-------|--------|----------|

|            | Type    |      | (pcs) | (mm)          | (mm)    | (mm)    | (mm)  | (mm)   | Quadrant |

| MK2552XAB  | SOP-8   | 8    | 4000  | 6.5±0.1       | 5.4±0.1 | 2.0±0.1 | 8±0.1 | 12±0.1 | Q1       |

| MK2552AXAB | SOP-8   | 8    | 4000  | 6.5±0.1       | 5.4±0.1 | 2.0±0.1 | 8±0.1 | 12±0.1 | Q1       |

| MK2552QXAB | SOP-8   | 8    | 4000  | $6.5 \pm 0.1$ | 5.4±0.1 | 2.0±0.1 | 8±0.1 | 12±0.1 | Q1       |

Figure 29. Tape Dimensions and Quadrant Assignments for PIN 1 Orientation in Tape

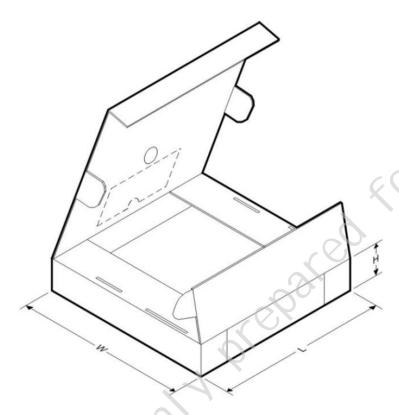

# 15. Tape and Reel Box Dimensions

| Device     | Package<br>Type | Pins | SPQ<br>(pcs) | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) |

|------------|-----------------|------|--------------|----------------|---------------|----------------|

| MK2552XAB  | SOP-8           | 8    | 8000         | 360            | 360           | 65             |

| MK2552AXAB | SOP-8           | 8    | 8000         | 360            | 360           | 65             |

| MK2552QXAB | SOP-8           | 8    | 8000         | 360            | 360           | 65             |

Figure 30. Box Dimensions