## **Ultra-Fast Turn-off Synchronous Rectifier Controller**

## 1. Description

The MK91816 is a compact secondary side synchronous rectifier controller and driver for high frequency and high-performance flyback converters. It is compatible with DCM, CCM and QR operations.

The MK91816 generates its own supply while used in high-side rectification, which eliminates the need of external supply generated by auxiliary winding of the transformer.

The extremely low 10ns turn-off propagation delay time and high sink current (~4A) capability of the driver improve SR V<sub>DS</sub> stress at CCM mode.

The unique VG clamping circuit works well to prevent VG from turning on by fast rising at VD pin with no VCC, that avoids the shoot through between primary side and secondary side during system startup even if the SR VCC is still below 2V.

## 2. Typical Applications

- AC/DC Adapters for Mobile Phone and Notebook

- High Power density AC/DC Power Supplie

### 3. Features

- Operates in a Wide Output Voltage Range Down to Zero Voltage

- Self-supply for Operation with Low Output Voltage and/or High-side Rectification without an Auxiliary Winding

- Gate Drive Clamp Voltage is Up to 9.5V

- 10ns Fast Turn-off and 25ns Turn-on Delay

- Programable Minimum on time to support wide frequency range

- VD/HVIN Pin Supports Negative Voltage Spikes Down to -3V

- VG Clamping Circuit works well for low Vth Value of MOSFET

- Optimized for up to 1MHz Frequency

- Supports Active Clamp Flyback with GaN FET or Super-junction MOSFET at Primary Side

- Supports DCM, QR and CCM Operations

- Supports both High-side and Low-side Rectification

- Adaptive Gate Drive for Maximum Efficiency

- SOT23-6 Package Available

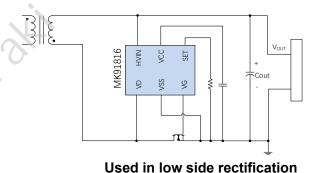

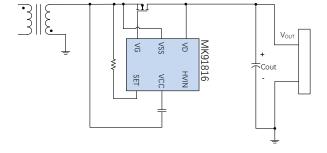

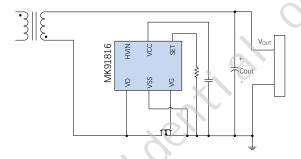

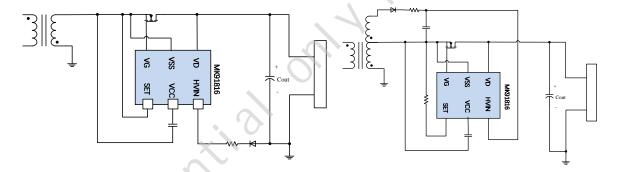

## 4. Simplified Application

Used in high side rectification

## 5. Ordering Information

| Ordering No. | Description            |

|--------------|------------------------|

| MK91816CSA   | SOT23-6, 3000 pcs/reel |

## 6. Pin Configuration and Marking Information

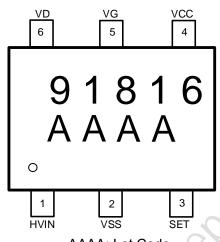

AAAA: Lot Code **SOT23-6**

### Absolute Maximum Ratings (1)

| VCC, VG, SET to VSS       | 0.3V to +20V                |

|---------------------------|-----------------------------|

| VD to VSS                 | 1V to +155V                 |

| HVIN to VSS               | 1V to +115V                 |

| VD to VSS                 | –3V to +165V <sup>(2)</sup> |

| HVIN to VSS               | 3V to 120V (2)              |

| Operating Junction Temper | rature40 to +150°C          |

| Lead Temperature          | + <b>260</b> ℃              |

| Storage Temperature       | 65°C to +150°C              |

#### Notes:

- (1) Exceeding these ratings may damage the device.

- (2) Repetitive pulse< 200ns

- (3) Measured on JESDSD51-7, 4 layers PCB

#### **Recommended Operation Conditions**

| VCC to VSS                                 | 3.6V to 10V  |

|--------------------------------------------|--------------|

| VD to VSS                                  | 0.7V to 150V |

| HVIN to VSS                                | 0.7V to 100V |

| Maximum Junction Temp. (T <sub>J</sub> ) . | +125°C       |

| Thermal Resistance (3)                     | <b>A</b>     |

| I nermai Resistance (5) | $\boldsymbol{\Theta}_{JA}$ | $\boldsymbol{\Theta}_{JC}$ |

|-------------------------|----------------------------|----------------------------|

| SOT23-6                 | 100                        | 66 °C/W                    |

## 7. Electrical Characteristics

T<sub>A</sub>=25°C, unless otherwise noted.

| Parameter                                                    | Symbol              | Conditions                                                                                                       | Min  | Тур  | Max  | Units    |

|--------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------|------|------|------|----------|

| Supply Management                                            |                     |                                                                                                                  |      |      |      |          |

| VCC UVLO Rising                                              | VCC_ON              |                                                                                                                  | 4.44 | 4.7  | 4.94 | <b>V</b> |

| VCC UVLO Falling                                             | VCC_OFF             |                                                                                                                  | 3.9  | 4.1  | 4.25 | V        |

| VCC UVLO Hysteresis                                          | VCC_HYST            |                                                                                                                  | 0.54 | 0.6  | 0.7  | V        |

| VCC Maximum                                                  | lvcc                | VCC=8V, VD=0V,<br>HVIN=20V                                                                                       | 70   |      |      | mA       |

| Charging Current                                             | IVCC                | VCC=5V, HVIN=0V, VD=20V                                                                                          | 40   | &C   |      | mA       |

| VCC Regulation                                               | VCC_REG             | VD= 0V, HVIN=14V                                                                                                 | 8.3  | 9.2  | 9.9  | V        |

| Voltage                                                      | VCC_REG             | VD= 10V, HVIN=0V                                                                                                 | 6    | 6.4  | 6.8  | V        |

| Operating Current                                            | I <sub>cc</sub>     | VCC=9V, $C_{LOAD}$ =2.2nF, $F_{SW}$ =100kHz                                                                      | 2.25 | 2.4  | 2.9  | mA       |

| Operating Current                                            | ICC                 | VCC=6.5V, C <sub>LOAD</sub> =2.2nF,<br>F <sub>SW</sub> =100kHz                                                   | 1.65 | 1.8  | 2.1  | mA       |

| Quiescent Current                                            | I <sub>q(VCC)</sub> | VCC=6.5V                                                                                                         | 140  | 190  | 230  | μΑ       |

| Mosfet Voltage Sensin                                        | g                   |                                                                                                                  |      | •    |      |          |

| V <sub>D</sub> –V <sub>SS</sub> Adjusting Voltage            | $V_{DS\_reg}$       |                                                                                                                  | -55  | -40  | -16  | mV       |

| Turn-On Threshold (V <sub>D</sub> –V <sub>SS</sub> )         | V <sub>ON_th</sub>  | 0),                                                                                                              | -300 | -250 | -200 | mV       |

| Turn Off Threshold (V <sub>D</sub> -V <sub>SS</sub> )        | $V_{OFF\_th}$       |                                                                                                                  | -19  | 0    | 15   | mV       |

| Turn-On Propagation Delay                                    | T <sub>D_on</sub>   | C <sub>LOAD</sub> = 0nF, VD step down<br>from 3V to -0.5V in 5ns,<br>measure VG rising to 1V                     | 10   | 25   | 40   | ns       |

| Turn-Off Propagation Delay                                   | $T_{D\_off}$        | C <sub>LOAD</sub> = 0nF, VD step up from<br>-0.5V to 3V in 5ns, measure<br>VG falling to 90% of V <sub>G-H</sub> | 4    | 10   | 15   | ns       |

| Turn On Blanking                                             | T <sub>B_ON</sub>   | R <sub>SET</sub> =0ohm, C <sub>LOAD</sub> = 2.2nF                                                                | 0.35 | 0.45 | 0.56 | us       |

| Time                                                         | T <sub>B_ON</sub>   | R <sub>SET</sub> =VCC, C <sub>LOAD</sub> = 2.2nF                                                                 | 0.9  | 1.05 | 1.2  | us       |

| Turn Off Blanking $V_{DS}$<br>Threshold in $T_{B\_ON}^{(1)}$ | $V_{B\_OFF}$        |                                                                                                                  |      | 2    |      | V        |

| Turn Off Blanking<br>Time                                    | T <sub>B_OFF</sub>  | C <sub>LOAD</sub> = 2.2nF                                                                                        | 250  |      | 350  | ns       |

| Gate Driver                                                  |                     |                                                                                                                  |      | •    |      |          |

| V <sub>G</sub> (Low)                                         | VGL                 | ILOAD= 100mA                                                                                                     |      | 0.1  | 0.3  | V        |

| V <sub>G</sub> (High)    |        | VGн   | ILOAD= 100mA | VCC- | VCC- | V   |

|--------------------------|--------|-------|--------------|------|------|-----|

|                          |        |       |              | 0.6  | 0.3  |     |

| Maximum                  | Source | n (O  |              |      |      |     |

| Current <sup>(1)</sup>   |        | IVGн  |              |      | 1    | Α   |

| Maximum                  | Sink   | IV/C  |              |      | 4    |     |

| Current <sup>(1)</sup>   |        | IVG∟  |              |      | 4    | Α   |

| Pull                     | Down   | Б     | II OAD 400mA |      | 0.50 | α ( |

| Impedance <sup>(1)</sup> |        | Rsink | ILOAD= 100mA |      | 0.53 | Ω   |

#### Note:

(1) Values are verified by characterization on bench, not tested in production

### 8. Pin Functions

| Pin # | Name | Description                                            |  |  |  |

|-------|------|--------------------------------------------------------|--|--|--|

| 1     | HVIN | HV Linear Regulator Input                              |  |  |  |

| 2     | VSS  | Ground, also used as FET source sense reference for VD |  |  |  |

| 3     | SET  | rogramming for GATE minimum turn on time               |  |  |  |

| 4     | VCC  | Linear Regulator Output, supply MK91816                |  |  |  |

| 5     | VG   | Gate drive output                                      |  |  |  |

| 6     | VD   | FET drain voltage sense; HV pulse LDO input            |  |  |  |

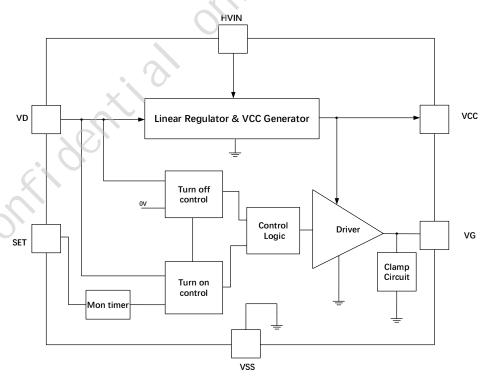

## 9. Block Diagram

Figure 1. Functional Block Diagram

### 10. Operation Descriptions

The MK91816 is an advanced secondary side synchronous rectifier controller and driver for high frequency and high performance flyback converters, which supports DCM, CCM and QR operations. The extremely low 10ns turn-off propagation delay time and high sink current ( $\sim$ 4A) capability of the driver improve SR V<sub>DS</sub> stress at CCM mode, particularly at the conditions of startup and V<sub>OUT</sub> shorting to ground. The unique VG clamping circuit works well to prevent VG from turning on by fast rising at VD pin with no VCC, that avoids the shoot through between primary side and secondary side during system startup.

#### **Vcc and Startup**

In order to reduce switching and conduction loss with wide range of voltage threshold Vth of MOSFETs, MK91816 provides the flexibility of different VG voltage. VCC is regulated at 9.5V which supplies MK91816 including VG when connect HVIN pin to a voltage source higher than 9.8V. Here the source for HVIN pin can be a DC voltage such as V<sub>OUT</sub> for low side rectification or an AC voltage such as the DRAIN of SR MOSFET. The average maximum charging current is 62mA while VCC is regulated from HVIN voltage source. Be noted the voltage applied to HVIN pin is self-limited with <100mA DC and 1A pulse after exceeding 120V, and VD pin is self-limited with <100mA DC and 1.5A pulse after exceeding 160V.

When the voltage on HVIN pin is below 9.5V but above 6.2V, VCC follows HVIN with dropout voltage depending on the load current at VCC, until HVIN drops to around 6.2V. Once HVIN drops around 6.2V, a 45mA current source from VD starts charging up VCC and regulating it at 6.2V.

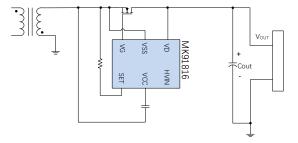

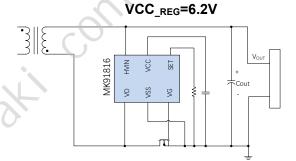

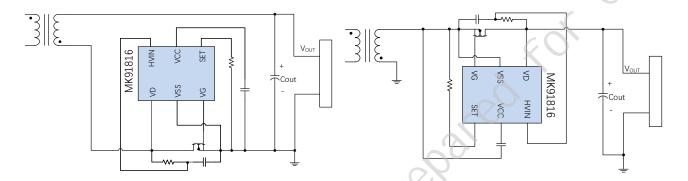

The typical system implementations with different bias connections are shown below. A 0.1uF to 1uF bypass capacitor is suggested at VCC pin.

Figure 2. Low-side Rectification 2,

Figure 3. High-side Rectification 2, VCC REG=6.2V

Figure 4. Low-side Rectification 3, VCC  $_{\rm REG}$ =6.2V to 9.5V $^{[1]}$

#### Note:

(1) In Low-side Rectification 4, VCC is supplied by VD and regulated at 6.2V if V<sub>OUT</sub> is lower than 6.2V; VCC is regulated at 9.5V through HVIN if V<sub>OUT</sub> voltage is larger than 9.8V; VCC is close to V<sub>OUT</sub> while V<sub>OUT</sub> is between 6.2V and 9.5V, which generated by HVIN path.

Pay attention to the voltage stress when connecting HVIN to Drain of SR MOS, as HVIN pin withstands less voltage rating than VD pin. To achieve 9V VCC, and lower HVIN voltage stress, below connections should be considered.

Figure 5. Low-side Rectification, VCC REG=9V

Figure 6. High-side Rectification, VCC\_REG=9V

Figure 7. High-side Rectification, VCC REG=9V

Figure 8. High-side Rectification, VCC\_REG=9V

#### **Conduction Phase**

After SR VG turns on, a minimum blanking time  $T_{B\_ON}$  is required to prevent the parasitic ringing from falsely turning off SR VG. The minimum turn-on blanking time programed by Rset for MK91816, during which the turn off threshold is increased to 2V. Right before  $T_{B\_ON}$  timer expires, MK91816 starts monitoring  $V_{DS}$  against a -40mV value to determine if VG needs to be slowly discharged. This operation adjusts  $V_{DS}$  of SR MOSFET to be around -40mV until the current through SR MOSFET drops to zero. In CCM mode, VG is prepositioned to be lower than VCC so that VG is turned off even faster; In DCM/QR mode, this  $V_{DS}$  adjusting design makes  $V_{DS}$  cross 0V exponentially faster, which combines with the 10ns turn-off propagation delay to make turn-off timing more accurately regardless of the accuracy of turn-off threshold.

#### **Turn Off Phase**

Within the minimum turn-on blanking time  $T_{B\_ON}$ ,  $V_{DS}$  turn-off threshold is 2V which is the same as  $V_{B\_OFF}$ . After the minimum turn-on blanking time  $T_{B\_ON}$ , the turn-off threshold is decided by  $T_{B\_ON}$ , that combines with extremely fast 10ns turn-off propagation delay and 4A VG pull-down (sinking) current, synchronous rectifier is able to be turned off not too early which causes more SR FET body diode conduction time and more negative turn-off ringing, or not too late which creates risk of shoot through between primary side and SR side in CCM mode.

#### **Minimum On Time Programming**

The turn on blanking time  $(T_{B\_ON})$  is programmed by SET pin,  $T_{B\_ON} = (20/3)^*(Rset(k)+60)$  ns, where Rset is in the range of 10k to 310k. Rset is connected between SET pin and VSS pin. when Rset is smaller than 10k,  $T_{B\_ON}$  is fixed to 400ns. when Rset is 310k,  $T_{B\_ON}$  is ~2.5us. If SET PIN is floating(or Rset≥340k), then  $T_{B\_ON}$  is around 1us.

## 11. PCB Layout Recommendations

Fidenti

The PCB layout guidance are shown below:

- 1. The trace from VG pin to the GATE of SR MOSFET needs to be as short as possible. The VSS pin to the SOURCE of SR MOSFET needs to route with short and wide trace

- 2. The sense loop (VD pin and VSS pin) is as small as possible

- In two-layer boards, avoid fast dv/dt traces underneath MK91816, such as the DRAIN of SR MOSFET network

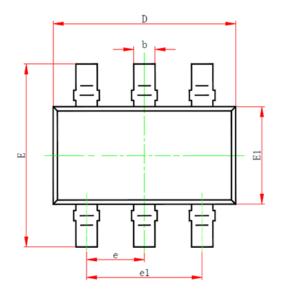

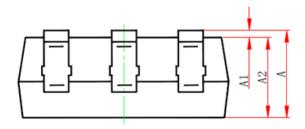

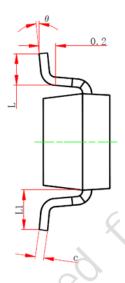

# 12. Package Information (SOT23-6)

| Symbol | Dimensions In Millimeters |        |  |  |  |

|--------|---------------------------|--------|--|--|--|

| Symbol | MIN                       | MAX    |  |  |  |

| Α      | 1.05                      | 1.25   |  |  |  |

| A1, 03 | 0.00                      | 0.10   |  |  |  |

| A2     | 1.05                      | 1.15   |  |  |  |

| b      | 0.30                      | 0.50   |  |  |  |

| С      | 0.10                      | 0.20   |  |  |  |

| D      | 2.82                      | 3.02   |  |  |  |

| E      | 2.65                      | 2.95   |  |  |  |

| E1     | 1.50                      | 1.70 × |  |  |  |

| е      | 0.95(BSC)                 |        |  |  |  |

| L      | 0.30                      | 0.60   |  |  |  |

| θ      | 0°                        | 8°     |  |  |  |

Figure 9. Package Information

# 13. Tape and Reel Information

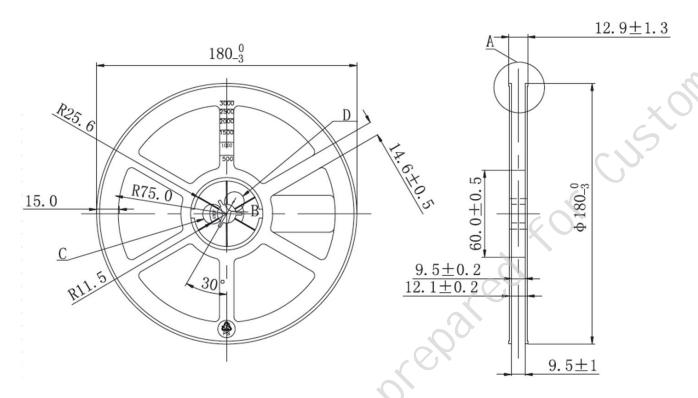

figure 10. reel dimensions

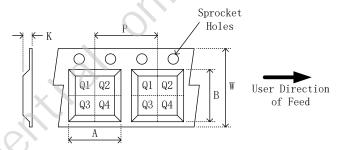

Figure 11. Tape Dimensions and Quadrant Assignments for PIN 1 Orientation in Tape

| Device     | Package   | Pins | SPQ   | А        | В        | K        | Р     | W     | Pin1             |

|------------|-----------|------|-------|----------|----------|----------|-------|-------|------------------|

| Device     | Type      |      | (pcs) | (mm)     | (mm)     | (mm)     | (mm)  | (mm)  | Quadrant         |

| MK91816CSA | SOT-23-6L | 6    | 3000  | 3.23±0.1 | 3.17±0.1 | 1.37±0.1 | 4±0.1 | 8±0.1 | Q <mark>3</mark> |

## 14. Tape and Reel Box Dimensions

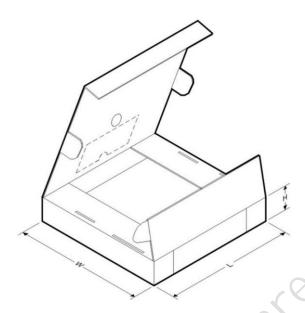

Figure 12. Box Dimensions

| Device     | Package Type | Pins | SPQ<br>(pcs) | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) |

|------------|--------------|------|--------------|----------------|---------------|----------------|

| MK91816CSA | SOT-23-6L    | 6    | 30000        | 203            | 203           | 195            |