## MK2780 Wide VCC Range HF QR Controller with GaN Integrated

### 1. Description

The MK2780 is a high frequency QR controller optimized for PD/Fast charge applications. Its wide VCC operating voltage range (9V-85V) allows it to cover PD/PPS from 3.3V-21V output range without the need to use additional VCC windings or linear step-down circuits.

In order to achieve high efficiency from universal line across different load, the MK2780 is selfadaptive to operate at DCM/QR. At light load, it will work in Burst mode to improve efficiency.

The MK2780 offers various protection features including output over-voltage protection (OVP), output over power protection (OPP), VCC overvoltage protection, Brown in/out, Secondary side SR short circuit protection (SSCP), and CS short protection.

## **Typical Applications**

- 65W AC/DC PD/Adapter

- High Power Density Power Supply

## Simplified Application VCC 2 8 D HVIN 1 VCC DRAIN 1 MK1205H DRAIN 2 10 GND DRAIN 3 COMP

#### 3. Features

- Built-in 700V 170mR GaN FET

- Wide VCC Operating Range (9V-85V)

- Operating Frequency up to 130kHz

- Proprietary Soft-start Scheme to Achieve Low SR Vds Stress

- Optimized Efficiency to Easily Meets Energy Efficiency Standards

- **CS Short Protection**

- **OPP/SSCP Protection**

- Brown in /Brown out Function

- VCC OVP/VO OVP Protection

- Support PPS Wide Range Output

- Tiny DFN6X8 Package

**MK2780**

## 5. Ordering Information

| Ordering No. | Description           |

|--------------|-----------------------|

| MK2780IDG    | DFN6X8, 3000 pcs/reel |

## 6. Package Reference

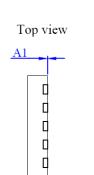

XXXXXXXX: Lot Code DFN6X8 Top View

#### 6.1 Absolute Maximum Ratings(1)

| VCC                  | 0.3V to +100V      |

|----------------------|--------------------|

| COMP, FB             | 0.3V to +5.5V      |

| CS                   | 0.7V to +5.5V      |

| EM                   | 0.7V to +5.5V      |

| DRAIN                | 3V to +700V        |

| I <sub>D</sub>       | 10A <sup>(2)</sup> |

| I <sub>DM</sub>      | 22A <sup>(3)</sup> |

| Junction Temperature | +155°C             |

#### 6.2 Recommended Operation Conditions

| VCC |                          | 9V to 85V |

|-----|--------------------------|-----------|

| Max | imum Junction Temp. (TJ) | +125°C    |

| 6.3 | Thermal Resistance(4)    |           |

| Α., |                          | 15°C/\\   |

#### Notes:

- (1) Exceeding these ratings may damage the device;

- (2) Tj = 125°C; The maximum continuous drain current is calculated based on the maximum allowable junction temperature;

- (3) Tc = 25 °C, Tpulse = 10 µs; Limit was extracted from characterization test, not measured during production;

- (4) Measured on JESDSD51-7, 4 layers PCB.

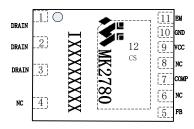

## 7. Pin Functions

| Pin #    | Name  | Description                                                                     |

|----------|-------|---------------------------------------------------------------------------------|

| 1、2、3    | DRAIN | HV Power GaN Drain                                                              |

| 4、6、8、11 | NC    | NC                                                                              |

| 5        | FB    | Auxiliary Voltage Sense                                                         |

| 7        | COMP  | Voltage Feedback                                                                |

| 9        | VCC   | Power Supply                                                                    |

| 10       | GND   | Ground                                                                          |

| 11       | EM    | Switching speed adjustment, connected to CS through a resistor and a fast diode |

| 12       | CS    | Current Sense Input                                                             |

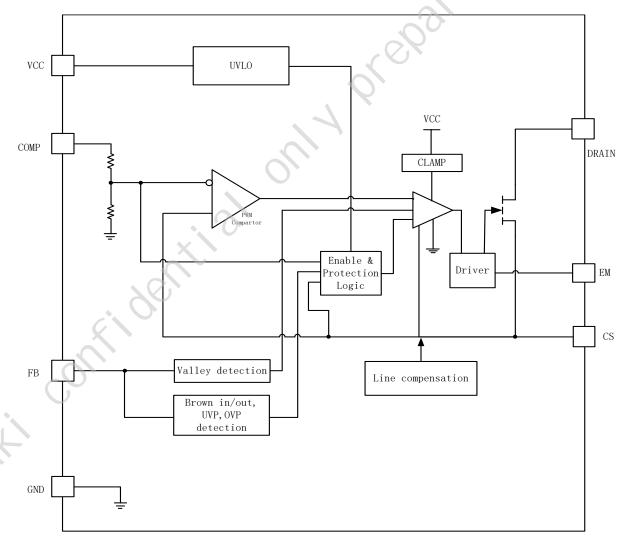

## 8. Block Diagram

Figure 1. Functional Block Diagram

### 9. Electrical Characteristics

VCC=12V,T<sub>A</sub>=25°C, unless otherwise noted.

| Parameter                                                           | Symbol                 | Conditions                                 | Min  | Тур                | Max  | Units  |

|---------------------------------------------------------------------|------------------------|--------------------------------------------|------|--------------------|------|--------|

| GaN Section                                                         |                        |                                            |      |                    |      |        |

| Maximum Drain Voltage                                               | V <sub>DS_max</sub>    |                                            | 700  |                    |      | V      |

| Static Drain to Source on Resistance                                | R <sub>DS(on)</sub>    | I <sub>D</sub> =1A                         |      | 170                | C    | mΩ     |

| <b>Supply Management Section</b>                                    |                        |                                            |      |                    |      | )      |

| VCC UVLO Rising                                                     | V <sub>CC_ON</sub>     |                                            | 15.5 | 17.2               | 19.9 | V      |

| VCC UVLO Falling                                                    | V <sub>CC_OFF</sub>    |                                            | 6    | 7.3                | 8.4  | V      |

| VCC UVLO Hysteresis                                                 | V <sub>CC_HYST</sub>   |                                            | 8.5  | 10                 | 11.2 | V      |

| VCC Startup Current                                                 | ISTARTUP               |                                            | 2    | 5                  | 8    | uA     |

| VCC Normal Operating Current                                        | I <sub>OP</sub>        | COMP=2V                                    | 0.3  | 0.6                | 1.5  | mA     |

| Burst Operating Current                                             | I <sub>BURST</sub>     | COMP=0V,<br>GATE=1nF to GND                | 240  | 290                | 340  | uA     |

| VCC OVP Threshold                                                   | V <sub>CC_OVP</sub>    |                                            | 87   | 93                 | 100  | V      |

| VCC Clamp Threshold                                                 | V <sub>CC_CLAMP</sub>  | . 4                                        | 89   | 102                | 110  | V      |

| Comp Input Section                                                  |                        |                                            |      |                    |      |        |

| COMP Open Voltage                                                   | V <sub>COMP_OP</sub>   | COMP Pin Open-<br>circuited                | 4    | 4.4                | 4.8  | V      |

| COMP Short-circuit Current                                          | I <sub>COMP_SHOR</sub> | COMP=0V                                    | 130  | 160                | 190  | uA     |

| Burst Mode Entry Voltage                                            | V <sub>BM_ET</sub>     |                                            | 0.27 | 0.30               | 0.33 | V      |

| Burst Mode Hysteresis                                               | $V_{BM\_HY}$           |                                            | 0.02 | 0.05               | 0.09 | V      |

| OPP Protection Threshold                                            | V <sub>OPP</sub>       |                                            | 2.8  | 3.0                | 3.2  | V      |

| OPP Deglitch Time*                                                  | $T_{D_{OPP}}$          |                                            |      | T <sub>SS</sub> *6 |      | ms     |

| Current Sense Input Section                                         |                        |                                            |      |                    |      |        |

| Soft Start Time of CS Threshold                                     | T <sub>SS</sub>        |                                            | 4    | 7                  | 10   | ms     |

| Secondary Rectifier Short-<br>circuit trigger voltage (OC<br>FAULT) | V <sub>SR_SH</sub>     |                                            | 1.1  | 1.2                | 1.3  | V      |

| SR Short-circuit Deglitch cycles*                                   |                        |                                            |      | 3                  |      | cycles |

| Cycle by Cycle Current Limit (low line)                             | V <sub>CS_CBCL</sub>   | V <sub>FB</sub> <1V,I <sub>FB</sub> =100uA | 0.79 | 0.85               | 0.91 | V      |

| Cycle by Cycle Current Limit(high line)        | V <sub>CS_CBCH</sub>  | V <sub>FB</sub> <1V,I <sub>FB</sub> =300uA | 0.56 | 0.63               | 0.7  | V          |

|------------------------------------------------|-----------------------|--------------------------------------------|------|--------------------|------|------------|

| CS Short Protection Threshold                  | $V_{\text{CS\_SH}}$   |                                            |      | 0.05               |      | V          |

| CS Short Deglitch cycles*                      | T <sub>CS_SH</sub>    |                                            |      | 3                  |      | cycles     |

| FB Input Section                               |                       |                                            |      |                    |      |            |

| Brown-in Detection Threshold                   | I <sub>BNI</sub>      |                                            | 78   | 94                 | 109  | uA         |

| Brown-out Detection Threshold                  | I <sub>BNO</sub>      |                                            | 69   | 85                 | 100  | uA         |

| Brown-out Deglitch Time*                       | T <sub>BL_BNO</sub>   |                                            |      | T <sub>SS</sub> *7 | C    | ms         |

| FB OVP Threshold                               | $V_{FB\_OVP}$         |                                            | 3.3  | 3.6                | 3.9  | V          |

| FB OVP Deglitch Time*                          | T <sub>BL_OVP</sub>   |                                            |      | 7. (               |      |            |

| FB UVP Threshold (Output Short)                | V <sub>FB_ST</sub>    |                                            | 0.17 | 0.20               | 0.23 | V          |

| FB UVP Threshold (Output Short) Deglitch Time* | $T_{BL\_ST}$          |                                            | (0)  | 7                  |      | cycles     |

| UVP Blanking Time after SS*                    | $T_{D\_ST}$           |                                            | 0.   | T <sub>SS</sub> *2 |      | ms         |

| FB High Threshold                              | $V_{FB\_H}$           | (8)                                        | 1.7  | 1.9                | 2.1  | V          |

| FB Middle Threshold                            | V <sub>FB_M</sub>     | 0                                          | 1    | 1.1                | 1.2  | V          |

| Control Law                                    |                       |                                            |      |                    |      |            |

| Normal Mode Frequency                          | F <sub>SW_max</sub>   |                                            | 110  | 130                | 150  | kHz        |

| Green Mode Frequency                           | F <sub>SW_green</sub> |                                            | 21   | 25                 | 29   | kHz        |

| Dithering Range*                               |                       | /                                          |      | ±6                 |      | %          |

| Dithering Period*                              |                       |                                            |      | 8                  |      | ms         |

| Maximum Toff Time                              | $T_{\text{off\_MAX}}$ |                                            | 80   | 110                | 140  | us         |

| Thermal Shutdown Threshold*                    | Th <sub>SD</sub>      |                                            |      | 155                |      | $^{\circ}$ |

| Thermal Shutdown Hysteresis*                   | Th <sub>SD_hys</sub>  |                                            |      | 30                 |      | $^{\circ}$ |

#### Note:

<sup>\*</sup> Guaranteed by design

#### 10. Operation Descriptions

#### Vcc and Startup

The MK2780's start-up current ISTARTUP is only ~5uA so that a large value of start-up resistor can be used to charge up VCC while minimizing power loss during start-up. Once VCC reaches above the  $V_{CC\ ON}$  (~17.2V) threshold, the MK2780 starts switching.

#### **Soft Start**

The MK2780 features an internal soft start T<sub>SS</sub> (~7ms) to reduce electrical stress in the power system during start-up. To further reduce voltage stresses from high peak current and high frequency switching, the MK2780 operates at optimized frequencies and control modes accordingly to the output voltages and the startup status of the synchronous rectifier controller.

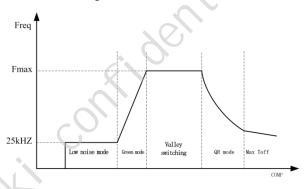

#### **Operation Curve**

The MK2780 has multiple working modes, which can be switched by monitoring the voltage change of COMP. Since the voltage change of COMP is consistent with the load change, the MK2780 can automatically switch to the optimal operating mode according to different load conditions. The operation curve of the MK2780 operating mode is shown as in Figure 2:

Figure 2: operation curve

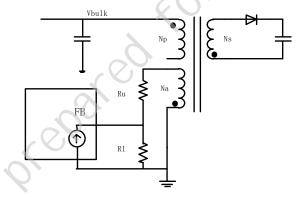

#### Brown in/ Brown out

When the power GaN is turned on, the voltage at auxiliary windings is negative, which makes Brown-in/Brown-out protection feasible detecting the current at FB pin. When the system

starts up, and the power GaN is turned on, the current flowing out of FB pin is equal to:

$$\frac{V_{BULK}*Na}{Ru*Np}$$

If this current is larger than I<sub>BNI</sub> for four switching cycles, the controller enables soft start. Otherwise Brown-in restart protection is triggered.

During normal operation, if the current at FB is less than I<sub>BNO</sub> for at least T<sub>BL BNO</sub> (~49ms), the controller enters Brown-out restart protection.

Figure 3: Brown in/Brown out

#### **Current Sense**

The MK2780 is current mode PWM controller. The voltage detected on CS pin is compared with the voltage loop feedback voltage inside the chip to determine the duty ratio. When COMP is at its maximum, the MK2780 also limits the peak current of the primary edge every switching cycle, and its maximum current limit value is V<sub>CS</sub> <sub>CBC</sub>/Rcs.

Due to the voltage of the drive current on the CS resistance and the influence of the converted capacitor C<sub>SW</sub> on the drain node, there will be a spike in the CS resistance at the moment when the driver is switched on. This spike could trigger PWM controller to falsely generate very narrow duty cycle pulse. Therefore, the leading-edge blanking time ~300ns was added to the CS sampling circuit inside the chip.

#### **Line Compensation**

The MK2780 uses the detected input line voltage through the current at FB pin to generate the offset voltage added on internal current signal to compensate the output OPP power level. This mechanism helps to achieve flat OPP power level over different input voltage.

#### Voltage Feedback Loop

COMP is the voltage loop feedback pin which is connected to TL431 output through opto-coupler. In order to support a wide COMP range, a ratio of 1/2.5 resistor divider is used before it goes into PWM comparator.

A ceramic capacitor is suggested to be placed parallel to the resistor which is series with optocoupler diode.

#### **FB Voltage Detection**

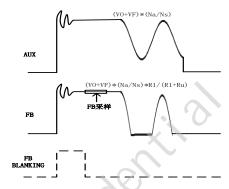

The MK2780 detects the transformer core demagnetization by monitoring the signal at the auxiliary windings through FB pin.

Figure 4: FB detection

After a period of demagnetization time (~1.4us) of the transformer, the FB sampling voltage is compared with different thresholds. The MK2780 can complete the following functions:

- Output over voltage protection (OVP): FB is above V<sub>FB\_OVP</sub> (~3.6V) for 7 switching cycles;

- Output under voltage protection (output short circuit protection): FB is below V<sub>FB\_ST</sub> (~0.2V) for 7 switching cycles;

- Based on the detected output voltage, the operating control curve is determined.

#### Valley Switching

After secondary side rectification is complete, the drain voltage starts oscillating with a frequency of approximately  $^{1}/_{2}\pi\sqrt{\cos s \times Lp}$ , where Lp is the inductance of primary winding of the transformer and Coss is capacitance on the drain of primary GaN. When the oscillation ringing is below 0V at the auxiliary winding, the MK2780 clamps the FB pin to 0V, and senses the current at the FB pin. When the current out of FB reaches a designed value, a "possible" valley is locked and the MK2780 turns on after propagation delay.

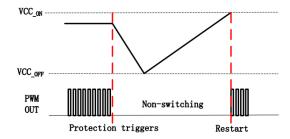

#### **Protection Function**

Reliable power supply system is achieved with restart protections including cycle-by-cycle current limit, over-power protection (OPP), output over-voltage protection, etc. Detailed protection features are described in the following sessions. The MK2780 protection triggers, will stop the drive, the VCC discharge current makes the VCC capacitor voltage drop. When the VCC voltage drops to  $V_{CC\_OFF}$  (~7.2V), the VCC capacitor starts charging and reaches  $V_{CC\_ON}$  (~17.2V), restarting the drive and completing the restart.

Figure 5: Restart mode

| MK2780 PROTECTION | MK2780 PROTECTION |

|-------------------|-------------------|

| FEATURES          | SCHEMES           |

| OPP               | RESTART           |

| VO_OVP            | RESTART           |

| VCC_OVP           | RESTART           |

| CS_SHORT          | RESTART           |

| SSCP              | RESTART           |

| FB_UVP (VO_SCP)   | RESTART           |

#### **Over Power Protection**

The OPP protection is achieved by monitoring COMP voltage. If COMP voltage is above  $V_{\text{OPP}}$  (~3V) for at least 6 times of soft-start time, i.e. Tss\*6 (~42ms), the MK2780 enters restart mode.

#### **Cycle by Cycle Current Limiting**

The current-mode controller compares the CS signal with the COMP signal cycle-by-cycle. However during an output short circuit or an open opto-coupler fault, the COMP voltage can rise excessively, leading to high peak currents and transformer saturation. To mitigate this, the MK2780 implements an additional protection scheme, which compares the CS voltage with VCS\_CBC cycle-by-cycle. After the blanking time of approximately 300ns, if the CS voltage reaches VCS\_CBC, the chip immediately halts the driver output.

# Secondary Side SR Short Circuit Protection

If the secondary side synchronous rectifier is short circuited, the peak current increases rapidly after the power GaN is turned on. Therefore, the protection is needed to react in much less wait time. The MK2780 reduces current sense blanking time to 90ns when the CS pin detects a voltage above V<sub>SR\_SH</sub> (~1.2V) threshold. It immediately stops the driver output. If this condition persists for three consecutive cycles, the MK2780 determines that a secondary SR short circuit has occurred, and it stops the driver

and enters the restart mode.

#### **CS Short Protection**

If CS still fails to reach  $V_{\text{CS\_SH}}$  (~0.05V) after 5us of primary GaN turning on, the MK2780 will force drive shutdown. If this condition occurs for three consecutive periods, the MK2780 enters restart mode.

#### Vcc OVP

Whenever the VCC voltage is higher than the OVP threshold voltage  $V_{CC\_OVP}(\sim 93V)$ , the output gate drive circuit will be shut down to stop the switching of the power GaN, and the MK2780 enters the restart mode.

#### **OTP**

The MK2780 provides internal over-temperature protection with a trigger point of ~155°C and a hysteresis temperature of ~30°C.

#### **Switching Speed Adjustment**

The EM pin is connected to the internal driver circuit and linked to the CS pin through external resistors and fast-recovery diodes, enabling the adjustment of GaN switching speed. In situations where high voltage stress on the SR MOSFET or EMI-related issues arise, external adjustments can be made using this configuration. Typically, the resistor value should be selected within the range of 0– $47\Omega$ . A  $10\Omega$  resistor in parallel with a 1N4148 fast-recovery diode is generally recommended to achieve optimal results.

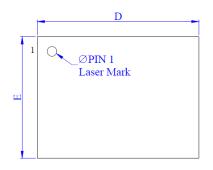

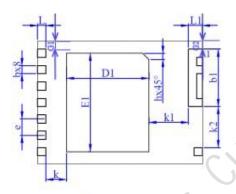

## 11. Package Information (DFN6X8)

Bottom view

Side view

| ·      |         |                      |       |  |  |  |  |

|--------|---------|----------------------|-------|--|--|--|--|

| Symbol | Din     | nensions In Millimet | ers   |  |  |  |  |

| Symbol | MIN     | NOM                  | MAX   |  |  |  |  |

| А      | 0.80    | 0.85                 | 0.90  |  |  |  |  |

| A1     | 0.00    | -                    | 0.05  |  |  |  |  |

| b      | 0.35    | 0.40                 | 0.45  |  |  |  |  |

| b1     | 2.70    | 2.80                 | 2.90  |  |  |  |  |

| D      | 7.90    | 8.00                 | 8.10  |  |  |  |  |

| D1     | 3.90    | 3.90 4.00            |       |  |  |  |  |

| E      | 5.90    | 6.00                 | 6.10  |  |  |  |  |

| E1     | 4.70    | 4.80                 | 4.90  |  |  |  |  |

| е      |         | 0.8 BSC              |       |  |  |  |  |

| h      | 0.20    | 0.30                 | 0.40  |  |  |  |  |

| k      |         | 0.8 MIN              |       |  |  |  |  |

| K1     |         | 1.7 MIN              |       |  |  |  |  |

| K2     | 1.8 MIN |                      |       |  |  |  |  |

| L      | 0.30    | 0.40                 | 0.50  |  |  |  |  |

| L1     | 0.575   | 0.675                | 0.775 |  |  |  |  |

| G1     | 0.35    | 0.40                 | 0.45  |  |  |  |  |

| G2     | 0.35    | 0.40                 | 0.45  |  |  |  |  |

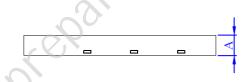

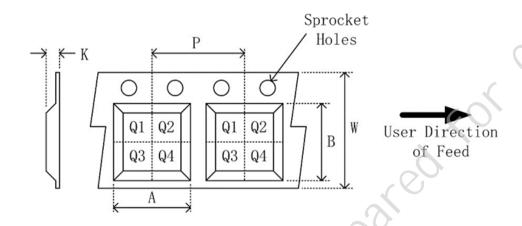

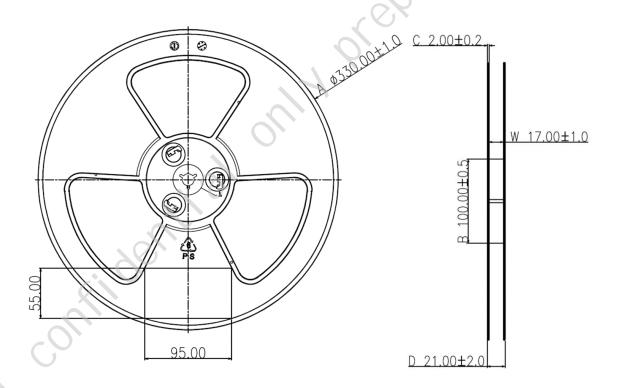

## 12. Tape and Reel Information

| Device    | Package<br>Type | Pins | SPQ<br>(pcs) | A<br>(mm) | B<br>(mm) | K<br>(mm) | P<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------|-----------------|------|--------------|-----------|-----------|-----------|-----------|-----------|------------------|

| MK2780IDG | DFN6x8-<br>11L  | 11   | 3000         | 6.3±0.1   | 8.3±0.1   | 1.0±0.1   | 8.0±0.1   | 16.0±0.3  | Q2               |

## 13. Tape and Reel Box Dimensions

| Device    | Bookaga Typa | Pins  | SPQ   | Length | Width | Height |

|-----------|--------------|-------|-------|--------|-------|--------|

| Device    | Package Type | FIIIS | (pcs) | (mm)   | (mm)  | (mm)   |

| MK2780IDG | DFN6x8-11L   | 11    | 6000  | 360    | 360   | 65     |