# Single-Channel Synchronous Rectifier Controller

### 1. Description

The MK1170-Q1 is a single-channel synchronous rectifier (SR) controller for flyback, forward and half-bridge converter. With appropriate gate drive method and independent sampling input, the MK1170-Q1 can achieve maximum efficiency under different load conditions.

The extremely low turn-off propagation delay time and high sink current (~4A) capability of the driver reduce SR MOSFET VDS stress. With 4A source current capability, the IC can control one or more paralleled N-Channel MOSFETs to emulate the behavior of Schottky diode rectifiers. The unique VG clamping circuit prevents VG from turning on by fast rising at VD pin under low VCC condition, that avoids the shoot through between primary side and secondary side during system startup. The advanced control strategy of MK1170-Q1 allows for stable SR operation over entire load range. The SYNC pin can directly turn off MOSFETs through signals from the secondary or primary controller. By using the MODE pin, MK1170-Q1 can freely switch between SR mode and DRIVER mode, making system applications more flexible.

### 2. Applications

- Automotive DC-DC converters

- High power industrial SMPS

- High performance server power supply

### 3. Features

- Wide VCC Voltage Range from 12V-26V

- Ultra-Low Quiescent Current <70uA</li>

- 22ns Fast Turn-off Propagation Delay Time

- VGA Clamping Circuit for Low Vth SR MOSFET

- Maximum Voltage at VD PIN 115V

- -3V Drain Voltage Spike Tolerance

- True Differential Inputs for VDS Sensing of SR MOSFET

- CCM Operation with SYNC Function

- Switch Freely Between DRIVER Mode and SR Mode

- 4A Source and Sink Output Peak Currents

- Enable Features and Cycle by Cycle MOT Check Circuit

- Available in ESOP-8 Package

- Qualified for Automotive Applications

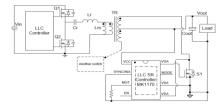

# 4. Typical Application

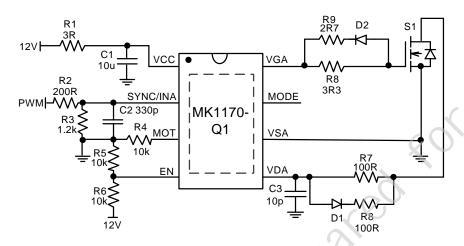

Figure 1. Typical Application Diagram

### 5. Order Information

| Order Part Number | Descriptions                |

|-------------------|-----------------------------|

| MK1170XAD-Q1      | ESOP-8, tape, 4000 pcs/reel |

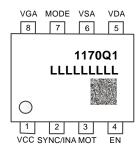

# 6. Pin Configuration and Functions

Figure 2. Pin Function (top view)

**Table 1. Pin Functions**

| Pin |          | Descriptions                                                             |

|-----|----------|--------------------------------------------------------------------------|

| NO. | Name     | Descriptions                                                             |

| 1   | VCC      | Supply voltage.                                                          |

| 2   | SYNC/INA | SYNC Input for direct turn off (SR mode); Input of driver (DRIVER mode). |

| 3   | MOT      | Minimum on time (SR mode).                                               |

| 4   | EN       | Enable.                                                                  |

| 5   | VDA      | MOSFET drain sense input (SR mode).                                      |

| 6   | VSA      | Ground, also used as MOSFET source sense input.                          |

| 7   | MODE     | Mode selection (SR or DRIVER).                                           |

| 8   | VGA      | MOSFET gate drive output.                                                |

|     | EspPad   | at VSA potential, use only for thermal dissipation.                      |

# 7. Specifications

## 7.1 Absolute Maximum Ratings (1)

| Symbol             | Parameter                         | MIN  | MAX | Units |

|--------------------|-----------------------------------|------|-----|-------|

| VCC                | supply voltage VCC                | -0.3 | 28  |       |

| VGA <sup>(2)</sup> | voltage on pin VGA (DC)           | -0.3 | 18  |       |

| VGA (=)            | voltage on pin VGA (Pulse)        | -2   | 18  | V     |

| VDA                | drain sense voltage VDA           | -1   | 105 | V     |

| VDA (3)            | drain sense voltage VDA           | -3   | 115 |       |

| SYNC/INA, EN, MODE | input voltage                     | -10  | 28  |       |

| TJ                 | operating junction temperature,   | -40  | 150 |       |

| T <sub>stg</sub>   | storage temperature               | -55  | 150 | °C    |

| T <sub>sld</sub>   | soldering temperature (10 second) | N    | 260 | C     |

#### Notes:

- (1) Stresses beyond the "ABSOLUTE MAXIMUM RATINGS" may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated in "RECOMMENED OPERATING CONDITIONS". Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- (2) Output pin not to be voltage driven.

- (3) Repetitive Pulse<200ns.

### 7.2 ESD Ratings

|                            | · 0                                              | Value      | Units |

|----------------------------|--------------------------------------------------|------------|-------|

| Electrostatic              | ESD Susceptibility all Pins (HBM) <sup>(1)</sup> | $\pm 2500$ | V     |

| discharge V <sub>ESD</sub> | ESD Susceptibility all Pins (CDM) (2)            | ±2000      | V     |

#### Notes:

- (1) ESD Susceptibility, Human Body Model "HBM", according to AEC-Q100-002.

- (2) ESD Susceptibility, Charged Device Model "CDM", according to AEC-Q100-011.

## 7.3 Recommended Operating Conditions

|             |                     |                                                   | MIN  | MAX | Units |

|-------------|---------------------|---------------------------------------------------|------|-----|-------|

|             |                     | VCC supply voltage                                | 12   | 26  | V     |

| Recommended | a a a mama a n da d | drain sense voltage VDA and VDB                   | -0.7 | 100 | V     |

|             |                     | Input voltage, SYNC/INA, MODE, EN                 | -5   | 20  | V     |

|             | peration Conditions | MOT pin resistor value                            | 5    | 75  | kΩ    |

|             |                     | operating junction temperature. (T <sub>J</sub> ) | -40  | 125 | °C    |

### 7.4 Thermal Information

| MERAKI<br>INTEGRATED   |                                     | N       | <u>//K1170-Q1</u> | • |

|------------------------|-------------------------------------|---------|-------------------|---|

| 4 Thermal Informa      | ition                               |         |                   |   |

|                        |                                     | Value   | Units             |   |

| ackage Thermal         | $\theta_{JA}$ (Junction to ambient) | 49      | °C/W              |   |

| Resistance (1)         | $\theta_{JC}$ (Junction to case)    | 15      | C/VV              |   |

| ote:                   |                                     |         |                   |   |

| ) Measured on JESD51-7 | , 4-layer PCB.                      |         |                   | 7 |

|                        |                                     |         |                   | • |

|                        |                                     |         |                   |   |

|                        |                                     |         |                   |   |

|                        |                                     | 6       | ),                |   |

|                        |                                     |         |                   |   |

|                        |                                     | ared fr |                   |   |

|                        |                                     | (2)     |                   |   |

|                        |                                     |         |                   |   |

|                        |                                     | 0.      |                   |   |

|                        |                                     |         |                   |   |

|                        |                                     |         |                   |   |

|                        | 0,                                  |         |                   |   |

|                        |                                     |         |                   |   |

|                        |                                     |         |                   |   |

|                        |                                     |         |                   |   |

|                        | 0)                                  |         |                   |   |

|                        |                                     |         |                   |   |

|                        |                                     |         |                   |   |

|                        | . 0                                 |         |                   |   |

|                        | X                                   |         |                   |   |

|                        |                                     |         |                   |   |

| 76                     |                                     |         |                   |   |

| . 0                    |                                     |         |                   |   |

#### Note:

### 7.5 Electrical Characteristics

-40°C  $\leq$  T<sub>A</sub> = T<sub>J</sub>  $\leq$  125°C. All Voltages are measured with respect to ground (pin 6). Currents are positive when flowing into the IC, unless otherwise specified.

| F                    | Parameter                                  | Test Conditions                        | MIN  | TYP  | MAX      | Units |

|----------------------|--------------------------------------------|----------------------------------------|------|------|----------|-------|

| Supply Vo            | Itage Management                           |                                        |      |      |          |       |

| V <sub>CC-ON</sub>   | VCC UVLO rising                            |                                        | 10.0 | 10.5 | 11.0     | V     |

| V <sub>CC-OFF</sub>  | VCC UVLO falling                           |                                        | 8.7  | 9.3  | 9.8      | V     |

| V <sub>CC-HYST</sub> | VCC UVLO                                   |                                        |      | 1.2  |          | V     |

|                      | hysteresis                                 |                                        |      | 1.2  |          | V     |

| Iccq                 | VCC quiescent                              | VCC = 9V, EN = 9V,                     |      | 6    | ),       |       |

|                      | supply current                             | SYNC/INA = 9V, VDA = 10V,              |      | 49   | 95       | μA    |

|                      |                                            | $R_{MOT} = 75k\Omega$                  |      |      |          |       |

|                      |                                            | VCC = 12V, EN = 0V,                    | _ (  | 175  | 280      | μA    |

|                      |                                            | SYNC/INA = 0V, VDA = 10V               |      | 173  | 200      | μΑ    |

| Icc                  | Operating supply                           | VCC = 12V, EN = 12V,                   | (0.  |      |          |       |

|                      | current                                    | $R_{MODE} = 75k\Omega$ , $VDA = 10V$ , | 2    | 0.33 | 0.52     | mA    |

|                      |                                            | SYNC/INA = 12V                         |      |      |          |       |

|                      |                                            | VCC = 12V, EN=12V,                     |      |      |          |       |

|                      |                                            | $C_{LOAD} = 2.2nF, MODE = 0V,$         |      | 3.5  | 5.4      | mA    |

|                      |                                            | VDA = 10V, $R_{MODE} = 75k\Omega$ ,    |      | 3.5  | 3.4      | 111/4 |

|                      |                                            | F <sub>SW</sub> =100kHz                |      |      |          |       |

| Synchron             | ous Rectification Se                       | nse Input                              |      |      |          |       |

| $V_{DS\text{-reg}}$  | $V_{DA} - V_{SA}$                          | VCC = 12V                              |      | -10  |          | mV    |

|                      | Adjusting voltage                          | VGG = 12V                              |      | -10  |          | 1110  |

| $V_{\text{ON-th}}$   | V <sub>DA</sub> – V <sub>SA</sub> Turn-on  | VCC = 12V                              | -350 | -290 | -250     | mV    |

|                      | threshold voltage                          | VOO - 12V                              | -330 | -230 | -230     | 1110  |

| $V_{OFF-th}$         | V <sub>DA</sub> – V <sub>SA</sub> Turn-off | VCC = 12V                              | 10   | 48   | 86       | mV    |

|                      | threshold voltage                          | VOO - 12V                              | 10   | 70   | 00       | 111 V |

| $T_{D\text{-}on}$    | Turn-on                                    | VCC = 12V, CLOAD = 0nF, VDA            |      |      |          |       |

|                      | propagation delay                          | step down from 5V to -0.8V,            |      | 167  | 220      | ns    |

|                      | time                                       | measure VGA rising to 1.5V             |      |      |          |       |

| $T_{D-off}$          | Turn-off                                   | VCC = 12V, CLOAD = 0nF, VDA            |      |      |          |       |

|                      | propagation delay                          | step up from -0.8V to 5V,              |      | 22   | 30       | ns    |

|                      | time                                       | measure VGA falling to 10.5            |      |      |          |       |

| Turn-on B            | lanking Time and Tu                        | rn-off Blanking Time                   | 1    |      | <b>.</b> | T     |

| $T_{B-on}$           | Turn-on blanking                           | $R_{MOT} = 30k\Omega$                  |      | 1.3  |          | He    |

|                      | time <sup>(1)</sup>                        | INNUT - JUN22                          |      | 1.0  |          | μs    |

| T <sub>B-on</sub>    | Turn-on blanking                           | $R_{MOT} = 75k\Omega$                  | 2.4  | 3.0  | 3.6      | He    |

|                      | time                                       | I VIVIOT - I ORSE                      | ۷.٦  | 0.0  | 0.0      | μs    |

| _                    | Turn off blooking                     |                           |          | <u> </u> |     |          |

|----------------------|---------------------------------------|---------------------------|----------|----------|-----|----------|

| $T_{B-off}$          | Turn-off blanking time <sup>(1)</sup> | $R_{MOT} = 30k\Omega$     |          | 1.65     |     | μs       |

| $T_{\text{B-off}}$   | Turn-off blanking                     | $R_{MOT} = 75k\Omega$     | 3.2      | 3.75     | 4.8 | μs       |

|                      | time                                  |                           |          |          |     | J        |

| $V_{\text{B-off}}$   | $V_{DA} - V_{SA}$ Turn-off            |                           |          |          |     |          |

|                      | threshold during                      |                           |          | 1.0      |     | VC       |

|                      | turn-on blanking                      |                           |          | 1.0      |     |          |

|                      | time <sup>(1)</sup>                   |                           |          |          |     |          |

| SYNC and             | INA Section                           |                           |          |          |     |          |

| V <sub>SIHI</sub>    | SYNC/INA                              |                           | 1.8      | 2.1      | 2.3 | V        |

|                      | Voltage High                          |                           | 1.0      | 2.1      | 2.3 | V        |

| V <sub>SILO</sub>    | SYNC/INA                              |                           | 0.9      | 1.1      | 1.0 | V        |

|                      | Voltage Low                           |                           | 0.9      | 1.1      | 1.3 | V        |

| V <sub>SIHYS</sub>   | SYNC/INA                              |                           |          | U ,      |     |          |

|                      | hysteresis                            |                           |          | 1        |     | V        |

| T <sub>SYON</sub>    | SYNC Turn-on                          | SYNC = high to low        | 70.      | 0.7      | 405 |          |

|                      | Prop. Delay                           | C <sub>LOAD</sub> = 2.2nF | ~        | 87       | 105 | ns       |

| T <sub>SYOFF</sub>   | SYNC Turn-off                         | SYNC = low to high        |          | 00       | 400 |          |

|                      | Prop. Delay                           | C <sub>LOAD</sub> = 2.2nF |          | 83       | 100 | ns       |

| T <sub>INON</sub>    | INA Turn-on Prop.                     | INA = high to low         | _        | 20       | 40  |          |

|                      | Delay                                 | $C_{LOAD} = 2.2nF$        | 5        | 22       | 40  | ns       |

| T <sub>INOFF</sub>   | INA Turn-off Prop.                    | INA = low to high         | _        | 07       | 4.5 |          |

|                      | Delay                                 | $C_{LOAD} = 2.2nF$        | 5        | 27       | 45  | ns       |

| T <sub>SYPWf</sub>   | Minimum SYNC                          | VCC = 16V, EN = 16V       |          |          |     |          |

|                      | Pulse Width                           |                           |          | 70       |     | ns       |

| T <sub>INPWf</sub>   | Minimum INA                           | VCC = 16V, EN = 16V,      |          |          |     |          |

|                      | Pulse Width                           | SYNC = 0V                 |          | 25       |     | ns       |

| Enable and           | d Mode Section                        |                           | <u> </u> |          |     | <u> </u> |

| V <sub>ENHI</sub>    | Enable Voltage                        |                           |          |          |     |          |

|                      | High                                  |                           | 1.8      | 2.1      | 2.3 | V        |

| V <sub>ENLO</sub>    | Enable Voltage                        |                           |          |          |     |          |

| LIVES                | Low                                   |                           | 0.9      | 1.1      | 1.3 | V        |

| V <sub>ENHYS</sub>   | Enable hysteresis                     |                           |          | 1        |     | V        |

| T <sub>ENON</sub>    | Enable Turn-on                        |                           |          | 04       |     |          |

|                      | Prop. Delay                           |                           |          | 21       |     | μs       |

| T <sub>ENOFF</sub>   | Enable Turn-off                       |                           |          | 000      |     |          |

|                      | Prop. Delay                           |                           |          | 390      |     | ns       |

| V <sub>MOHI_SR</sub> | MODE Voltage                          |                           | 4.0      | 0.4      | 0.0 |          |

| _                    | High (SR mode)                        |                           | 1.8      | 2.1      | 2.3 | V        |

| V <sub>MOLO_DR</sub> | MODE Voltage                          |                           | 0.9      | 1.1      | 1.3 | V        |

|                         | Low (DRIVER mode)                     |                                                            |    |      |     |    |

|-------------------------|---------------------------------------|------------------------------------------------------------|----|------|-----|----|

| V <sub>MOHYS</sub>      | MODE hysteresis                       |                                                            |    | 1    |     | V  |

| T <sub>MOSR</sub>       | SR Mode Prop.<br>Delay                |                                                            | 7  | 11   | 15  | μs |

| T <sub>MODR</sub>       | DRIVER Mode<br>Prop. Delay            |                                                            | 8  | 12   | 17  | μs |

| Gate Drive              | er                                    |                                                            | •  |      |     |    |

| V <sub>G-H</sub> (high) | Gate High Voltage                     | VCC = 16V,<br>$C_{LOAD}$ = 10nF, $R_{LOAD}$ = 10k $\Omega$ | 11 | 12   | 13  | V  |

| V <sub>G-L</sub> (low)  | Gate Low Voltage                      | I <sub>GATE</sub> = 100mA, VCC = 12V                       |    | 0.06 | 0.1 | V  |

| I <sub>VG-H</sub>       | Maximum source current <sup>(1)</sup> |                                                            |    | 4    |     | Α  |

| I <sub>VG-L</sub>       | Maximum sink current <sup>(1)</sup>   |                                                            |    | 4    |     | Α  |

| R <sub>sink</sub>       | Pull-down impedance                   | I <sub>GATE</sub> = 100mA                                  | 5  | 0.6  |     | Ω  |

#### Note:

<sup>(1)</sup> Values are verified by characterization on bench, not tested in production.

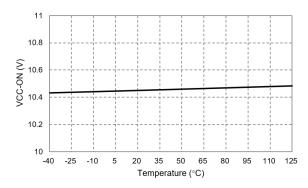

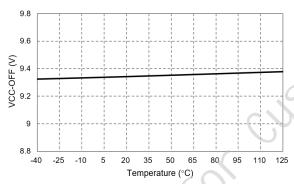

## 7.6 Typical Characteristics

Figure 3. VCC UVLO Rising vs Temperature

Figure 4. VCC UVLO Falling vs Temperature

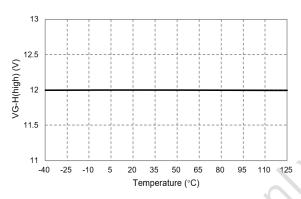

Figure 5. Gate High Voltage vs Temperature

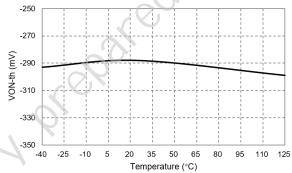

Figure 6.  $V_{DA} - V_{SA}$  Turn-on Threshold Voltage vs Temperature

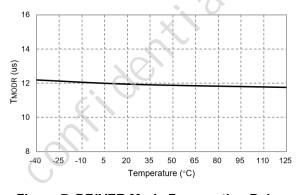

Figure 7. DRIVER Mode Propagation Delay

Time vs Temperature

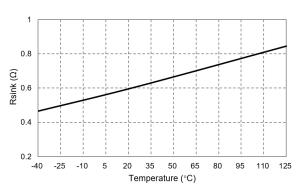

Figure 8. Pull-down Impedance vs

Temperature

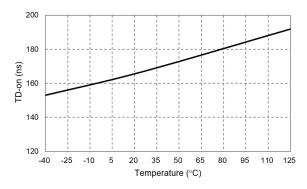

Figure 9. Turn-on Propagation Delay Time vs Temperature

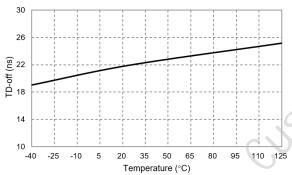

Figure 10. Turn-off Propagation Delay Time vs Temperature

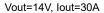

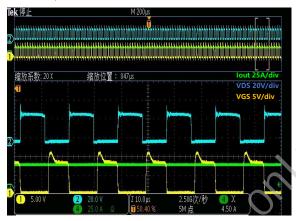

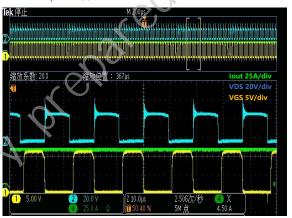

Vout=14V, Iout=50A

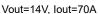

Figure 11. Operation in 2kW LLC Converter

Figure 12. Operation in 2kW LLC Converter

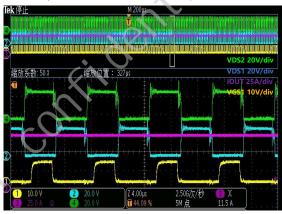

Vout=14V. lout=140A

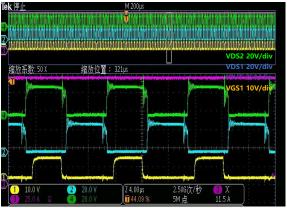

Figure 13. Operation in 2kW LLC Converter

Figure 14. Operation in 2kW LLC Converter

## 8. Detailed Description

#### 8.1 Overview

The MK1170-Q1 is a single-channel synchronous rectifier controller capable of driving N-Channel power MOSFETs in isolated resonant, flyback and forward converters. This controller has a differential sampling input to detect the voltage difference between the drain and source of SR MOSFET.

The gate voltage is adjusted consistently with the VDS voltage, which makes the chip easy to use. The unique VG clamping circuit works well to prevent VG from turning on by quickly rising at the VD pin with no VCC voltage. Extremely low turn-off propagation delay time and high sink current (~4A) capability of the driver reduce SR MOSFET VDS stress.

The advanced control scheme of MK1170-Q1 allows for stable SR operation over entire load range. The SYNC pin can directly turn off MOSFETs through signals from the secondary or primary controller. By using the MODE pin, MK1170-Q1 can freely switch between SR mode and DRIVER mode, making system applications more flexible.

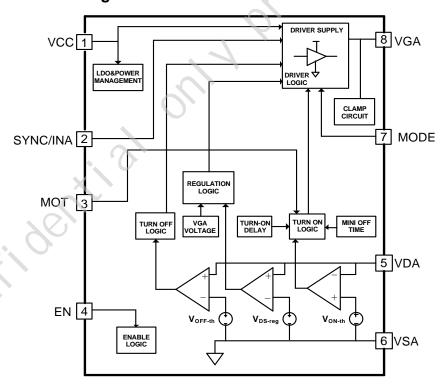

### 8.2 Functional Block Diagram

Figure 15. Block Diagram

### 8.3 Feature Description

#### 8.3.1 VCC Power Supply and Undervoltage Lockout

The MK1170-Q1 operates from a supply voltage of 12V to 26V. This feature makes MK1170-Q1 suitable for a variety of application scenarios. For the best performance, use a typical 0.1uF decoupling capacitor as close as possible between the VCC and VSA pins of MK1170-Q1. A VCC bypass capacitor (1uF to 10uF) in parallel to the decoupling capacitor is also recommended to reduce noise ripple during switching.

MK1170-Q1 has an internal undervoltage lockout (UVLO) protection feature in the VCC supply circuit blocks. When the voltage on the VCC pin exceeds  $V_{\text{CC-ON}}$ , the controller leaves the UVLO state. When VCC voltage drops to below  $V_{\text{CC-OFF}}$ , the controller re-enters the UVLO state.

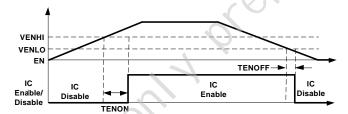

#### 8.3.2 Enable Function

The EN pin is used to disable the IC by pulling the voltage level below  $V_{\text{ENLO}}$  and after a  $T_{\text{ENOFF}}$  delay. When the IC is disabled, all switching functions will be disabled and the gate will be inactive. When the voltage of EN pin is higher than  $V_{\text{ENHI}}$ , and after a  $T_{\text{ENON}}$  delay, the IC is enabled. The timing diagram is shown on Figure 16.

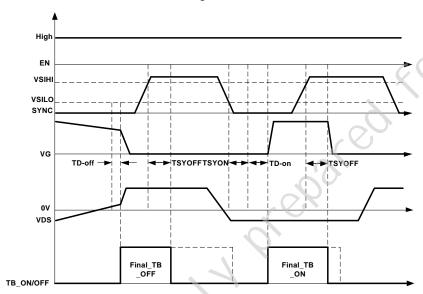

Figure 16. Enable Function Timing Diagram

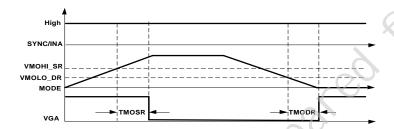

#### 8.3.3 Mode Function

Using the MODE pin, MK1170-Q1 can freely switch between SR mode and DRIVER mode. When the MODE pin floating or MODE pin voltage is higher than  $V_{\text{MOHI\_SR}}$  and after a  $T_{\text{MOSR}}$  delay, MK1170-Q1 operates in SR mode. In SR mode, SYNC, MOT and VDA functions are effective. The gate voltage is adjusted consistently with the MOSFET VDS voltage.

The DRIVER mode is enabled by pulling the MODE pin voltage level below  $V_{\text{MOLO\_DR}}$  and after a  $T_{\text{MODR}}$  delay. In DRIVER mode, INA function is effective, in which the gate output VGA follows the INA signal that is the non-inverting input of the MK1170-Q1 device. The timing diagram is shown on Figure 17.

Figure 17. Mode Function Timing Diagram

#### 8.3.4 MOT Function

In SR mode, the MOT programming pin controls the amount of turn-on blanking time and turn-off blanking time. After SR MOSFET turns on, a turn-on blanking time  $T_{B-on}$  is required to prevent the IC from falsely turning off SR MOSFET by parasitic ringing. During the turn-on blanking time, the turn-off threshold increases to  $V_{B-off}$ .

After SR MOSFET turns off, a minimum turn-off blanking time T<sub>B-off</sub> is required, which helps to reduce the chances of false triggering in DCM. The turn-on blanking time is programmed between 200ns and 3us (typical) by using a resistor referenced to VSA according to the following formula:

$$R_{MOT} \approx 2.5 * 10^10 * T_{B-on}$$

$T_{B-off} \approx 1.3 * T_{B-on}$

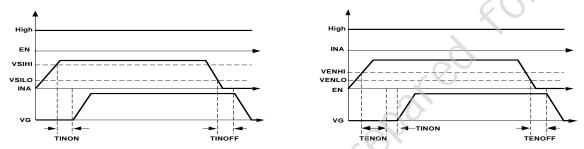

#### 8.3.5 SYNC/INA Function

SYNC/INA is a multi-function pin. In SR mode, SYNC function is effective, which can directly turn-off the SR MOSFET by an external signal. The gate output VGA is low when SYNC voltage is higher than V<sub>SIHI</sub> threshold. The propagation delay from SYNC goes high to gate turns off is 100ns maximum. The gate turns off by SYNC signal is a dominant control, which overrides the turn-on blanking time and turn-off blanking time control.

In DRIVER mode, the gate output VGA is controlled by INA signal directly, which is typically an external PWM control signal. The logic level thresholds are TTL compatible, which is conveniently driven by PWM control signal derived from 3.3V and 5V digital power controller devices. The INA and EN function timing diagram is shown on Figure 18.

Figure 18. INA and EN Function Timing Diagram

#### 8.3.6 SR Conduction Phase

When the IC is enabled and in SR mode, SYNC function is effective. The gate driver output of MK1170-Q1 is turned on when the SYNC voltage is below  $V_{SILO}$  and lasts a  $T_{MODR}$  delay, and the absolute voltage difference of SR MOSFET VDS (VDA-VSA) is greater than  $V_{ON-th}$  with VDS being negative.

After this, the MK1170-Q1 goes into regulation mode, and adjusts the VDS of SR MOSFET to be around  $V_{DS-reg}$  until the current through SR MOSFET drops to zero. The SR mode control timing diagram is shown on Figure 19.

#### 8.3.7 SR Turn-Off Phase

After the turn-on blanking time  $T_{B\text{-on}}$ , the turn-off threshold of VDS is set to around  $V_{\text{OFF-th}}$ . With a suitable VDS regulation and turn-off scheme, the MK1170-Q1 keeps SR MOSFET as much as possible to prevent it from turning off prematurely and conducting current through body diode for too long of time.

With an extremely fast turn-off propagation delay and ~4A pull-down (sink) current, the MK1170-Q1 is rapidly turned off when the current through the external SR MOSFET reaches zero.

Figure 19. SR Mode Control Timing Diagram

ONE GENTI

Stome

## Application and Implementation

### 9.1 Typical Applications

Figure 20. MK1170-Q1 Reference Design Circuit

### 9.2 Design Procedure

#### 9.2.1 **Supply Voltage**

The supply voltage applied to the controller VCC pin should never exceed the absolute maximum ratings. Higher supply voltages require consideration of chip power dissipation and junction temperature (See Section 9.2.4). In some scenarios where the output bus voltage is high (for example, applications with outputs greater than 36V), a high voltage LDO must be used so that the VCC pin does not exceed the absolute maximum ratings and reduces the power dissipation of the internal LDO.

MK1170-Q1 reference design circuit is shown in Figure 20, connecting a low-ESR ceramic decoupling capacitor (C1) between 1µF and 10µF from VCC to VSA for stability. The choice of decoupling capacitor voltage rating should also depend on the VCC voltage. Place the capacitor (C1) as close as possible to the MK1170-Q1 VCC and VSA pins.

#### **Peak Source and Sink Current** 9.2.2

To reduce the switching losses and stress of the SR MOSFET, the switching speed of the MOSFET during turn-on and turn-off should be considered. The chip should be able to provide the required peak current for achieving the targeted switching speeds with the targeted power MOSFET. The maximum source and sink currents of the MK1170-Q1 have been provided.

For system applications, adding resistor R8 (such as  $1\Omega$  or  $4.7\Omega$ ) between the gate of MOSFET and the VGA controls the switching speed of the MOSFET. Add diodes D2 as well as resistors R9. Keep the value of the resistor at  $0\Omega$  to achieve the fastest turn-off time.

### 9.2.3 Design of VDA Filtering Circuit

There are different circuit designs in different application systems. In SR mode,  $V_{\text{ON-th}}$  and  $V_{\text{OFF-th}}$  are important parameters, which determines the output of the gate driver. When VDS falls below  $V_{\text{ON-th}}$ , the gate driver output turns on the SR MOSFET. During regulation mode, MK1170-Q1 adjusts the VDS of SR MOSFET to be around  $V_{\text{DS-reg}}$  until the current through the SR MOSFET drops to zero. The driver will immediately shut down, when the VDS voltage exceeds  $V_{\text{OFF-th}}$ . If really needed, the detection value of VDS may be slightly fine-tuned by adding the filtering circuit (C3, R7, R8 and D1) between the drain of the MOSFET and VDA. Among them, C3 and R7 increase the turn-off delay of SR MOSFET, and the C3, R8 and D1 add SR MOSFET turn-on delay.

### 9.2.4 Power Dissipation

The chip power consumption and junction temperature must be considered. The chip will be damaged, if these two parameters are too large. The total power consumption (P<sub>DIS</sub>) is estimated by the following formula:

$$P_{DIS} = P_{DRV} + P_P$$

The gate power (PDRV) needs to be calculated first. It is calculated based on the formula:

$$P_{DRV} = (Q_q - Q_{qd}) \times f_{smax} \times V_{CC}$$

Where  $(Q_g-Q_{gd})$  is the total gate charge for SR MOSFET,  $f_{smax}$  is the maximum switching frequency, and  $V_{CC}$  is the supply voltage. The power consumption  $P_p$  (without gate charge) must also be included, as shown below:

$$P_P = I_{CC} \times V_{CC}$$

$I_{CC}$  is the normal operating supply current without gate charging. The operating junction temperature  $(T_{JOP})$  at a given ambient temperature  $(T_A)$  can be estimated according to the formula:

$$T_{IOP} = \theta_{IA} \times P_{DIS} + T_A$$

$\theta_{\text{JA}}$  is the junction-to-ambient thermal resistance.

#### 9.2.5 MOSFET Selection

The voltage stress of SR MOSFET on LLC topology, without considering the ringing voltages, must be twice of the output voltage. However, due to the switching noises when MOSFET is turned off, there is always extra voltage stress. To ensure enough design margin, the selection of VDS voltage rating for MOSFEET is important. It is recommended to ensure a margin of at least 3 times the output voltage.

Due to the adjusting voltage threshold and driver ability of the synchronous rectifier controller, the selection of the power MOSFETs is a trade-off between RDS(ON) and Qg. Choosing the appropriate Qg value is also very important. A larger Qg will reduce the on/off speed and result in greater switching loss. Therefore, it is necessary to consider the on/off speed and switching loss. MOSFETs with smaller RDS (ON) will touch the adjusting voltage threshold at higher current, so that the power MOSFET cannot be fully turned on due to lower gate voltage. Therefore, the

MK1170-Q1 v0.8 www.meraki-ic.com 16

Specifications Subject to Change without notice © 2024 Meraki IC. Confidential. Classified: Authorized Customer Only

conduction loss reduction barely observed, and the benefit of the lower RDS (ON) MOSFET is not obvious. It is recommended to calculate the appropriate Rdson using the following formula:

$$Rdson = \frac{Vdsreg * \Pi}{2\sqrt{2} * Ioutmax}$$

For example, the typical value Vdsreg of MK1170-Q1 is -10mV. In applications where the maximum output current loutmax is 20A, Rdson can be calculated:

$$Rdson = \frac{10mV * \Pi}{2\sqrt{2} * 20A} \approx 0.56m\Omega$$

the RDS(ON) of the MOSFET is recommended to be no lower than  $0.56m\Omega$ .

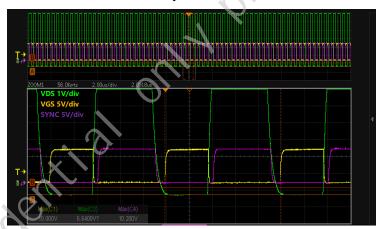

#### 9.2.6 **SYNC Signal Participates in SR Control**

The working waveform with SYNC signal is shown in Figure 21, where the purple line represents the SYNC signal, the green line represents the MOSFET VDS signal, the yellow line represents the gate output signal. The gate output must be low when SYNC voltage is higher than V<sub>SIHI</sub> threshold. Only when the SYNC voltage is below the V<sub>SILO</sub> threshold, MK1170-Q1 begins to detect and determine whether the VDS voltage is below the turn-on threshold, if so, the gate output is high. When the VDS voltage is detected to be above the turn-off threshold, even if the SYNC signal is still low, the MOSFET will immediately turn off.

Figure 21. MK1170-Q1 Reference Working Waveform

## 10. Power Supply Recommendations

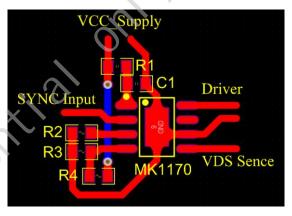

## 11. Layout

#### 11.1 **Layout Guidelines**

To achieve high performance of the MK1170-Q1, the following layout tips must be followed.

- Use separate clean traces for VCC and VSA pins.

- At least one low-ESR ceramic bypass capacitor(100nF) must be used. Place the capacitor as close as possible to the VCC and VSA pins.

- The VSA pin on the ground plane needs to route with a short and wide trace.

- 4. Use separate traces for source sense pin (VSA).

- Keep the differential sampling inputs (VDA/VSA) to MOSFET drain/source pins as short as possible.

- Keep the loop area of the differential sampling inputs (VDA/VSA) to MOSFET drain/source 6. pins as small as possible.

- 7. Avoid placing the VDA, VSA and SYNC traces close to any other high dV/dT traces that would induce significant noise into the high impedance leads.

- The trace from the VGA pin to the gate of the SR MOSFET needs to be as short as possible.

#### 11.1 Layout Example

Figure 22. MK1170-Q1 Layout Example

# 12. Device and Documentation Support

- 12.1 Device Support

- 12.2 Documentation Support

- 12.3 Receiving Notification of Documentation Updates

- 12.4 Support Resources

- 12.5 Trademarks

### 12.6 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Meraki Integrated recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

Meraki al

# 13. Mechanical, Packaging

# 13.1 ESOP-8 Package Size

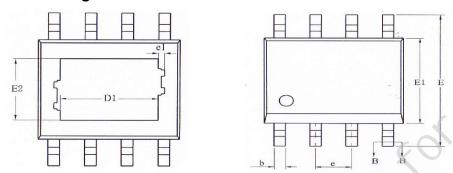

Figure 23. ESOP-8 Top View

Figure 24. ESOP-8 Side View

| SYMBOL   | Dimensions In Millimeters |      |  |  |  |

|----------|---------------------------|------|--|--|--|

| STIVIDOL | MIN                       | MAX  |  |  |  |

| Α        | -                         | 1.65 |  |  |  |

| A1       | 0.05                      | 0.15 |  |  |  |

| A2       | 1.30                      | 1.50 |  |  |  |

| b        | 0.39                      | 0.47 |  |  |  |

| С        | 0.20                      | 0.24 |  |  |  |

| D        | 4.80                      | 5.00 |  |  |  |

| Е        | 5.80                      | 6.20 |  |  |  |

| E1       | 3.80                      | 4.00 |  |  |  |

| D1       | 3.1F                      | REF  |  |  |  |

| E2       | 2.21REF                   |      |  |  |  |

| е        | 1.270(BSC)                |      |  |  |  |

| L        | 0.5                       | 0.8  |  |  |  |

| θ        | 0°                        | 8°   |  |  |  |

#### Note:

(1) This drawing is subject to change without notice

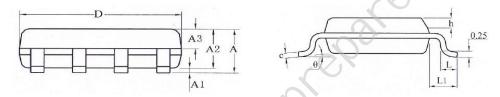

#### 13.2 **ESOP-8 Recommended Land Pattern**

Figure 25. ESOP-8 Recommended Land Pattern

#### Notes: (continued)

- (1) All linear dimensions are in millimeters.

- (2) It is recommended that vias under paste be filled, plugged or tented.

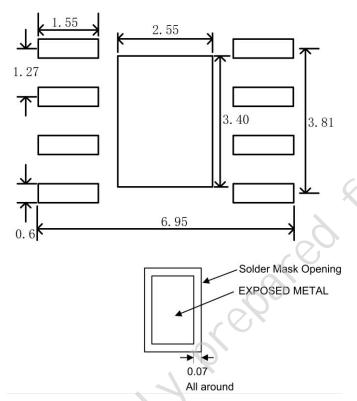

# 14. Reel and Tape Information

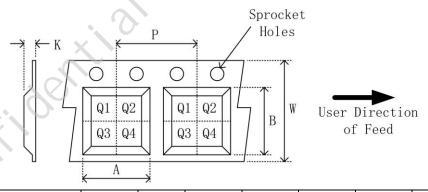

Figure 26. Reel Dimensions

|  | Device           | Package | Pins  | SPQ   | Α       | В       | K       | Р     | W      | Pin1     |

|--|------------------|---------|-------|-------|---------|---------|---------|-------|--------|----------|

|  |                  | Type    | F1113 | (pcs) | (mm)    | (mm)    | (mm)    | (mm)  | (mm)   | Quadrant |

|  | MK1170XAD<br>-Q1 | ESOP-8  | 8     | 4000  | 6.5±0.1 | 5.4±0.1 | 2.0±0.1 | 8±0.1 | 12±0.1 | Q1       |

Figure 27. Tape Dimensions and Quadrant Assignments for PIN 1 Orientation in Tape

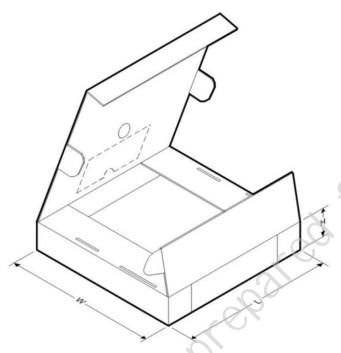

# 15. Tape and Reel Box Dimensions

| Device       | Package | Pins  | SPQ   | Length | Width | Height |

|--------------|---------|-------|-------|--------|-------|--------|

|              | Type    | FIIIS | (pcs) | (mm)   | (mm)  | (mm)   |

| MK1170XAD-Q1 | ESOP-8  | 8     | 8000  | 360    | 360   | 65     |

Figure 28. Box Dimensions