## 4-A, 7-A Peak, 5.7kV<sub>RMS</sub> Isolated Dual-Channel Gate Driver

# 1. Description

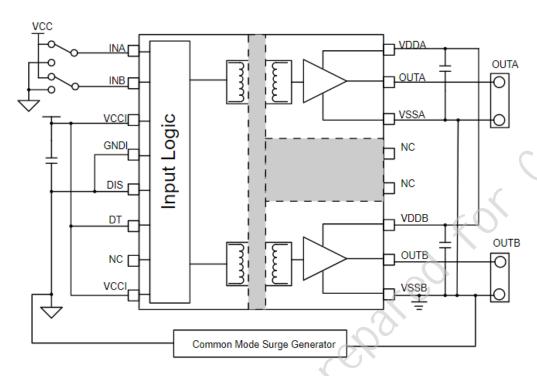

The MD18023A/B/C is an isolated dual channel gate driver family designed with 4-A source current and 7-A sink current to drive IGBTs, Si and SiC MOSFETs.

The device can be configured as two low-side drivers, two high-side drivers and a half bridge driver. The input side is isolated from the output side by 5.7kVRMS isolation barrier with a minimum of 200-V/ns common mode transient immunity (CMTI).

The inputs can handle -10V to 26V DC, which increases robustness against ringing from parasitic inductance of long routing traces.

Other features include resistor programmable dead time (DT PIN) control, disable feature to shutdown both outputs, and UVLO for all supplies.

# 2. Applications

- Isolated AC-DC and DC-DC power supplies

- Server, telecom, datacom, and industrial infrastructures.

- PV Inverters

- HEV and EV battery chargers

#### 3. Features

- Universal: Dual Low-side, Dual High-side, and Half Bridge Driver

- 4-A Source and 7-A Sink Peak Currents

- CMTI greater than 200V/ns

- Input Pins Can Tolerate -10V to 26V, Independent of Supply Voltage Range

- Fast Disable for Power Sequencing

- TTL Compatible Inputs

- Safety-related Certifications:

- (1) 8000-VPK reinforced Isolation per EN 60747-17

- (2) 4242-VPK based Isolation per EN 60747-17

- (3) SOW16:5.7kVRMS isolation for 1minute per UL 1577

- (4) SOP16: 3kVRMS isolation for 1minute per UL 1577

- (5) CQC certification per GB4943.1-2022

- Available in SOP16 and SOW16 packages

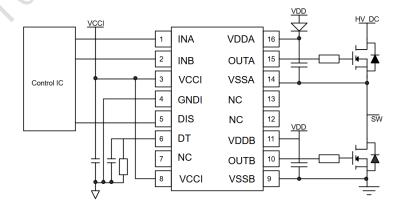

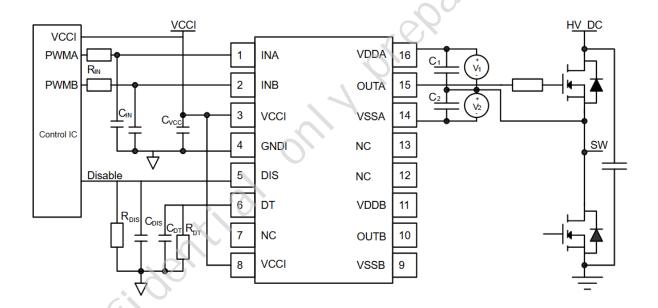

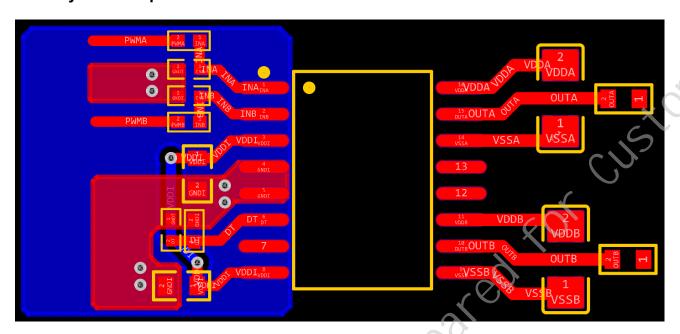

# 4. Typical Applications

**Figure 1.Typical Application Diagram**

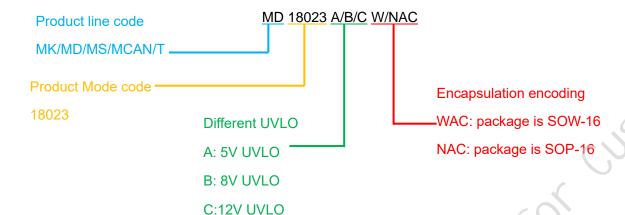

#### 5. Order Information

| Order Code  | UVLO | DT  | EN/DIS | Package | Pins | SPQ (pcs) |

|-------------|------|-----|--------|---------|------|-----------|

| MD18023AWAC | 5V   | YES | DIS    | SOW-16  | 16   | 1500      |

| MD18023BWAC | 8V   | YES | DIS    | SOW-16  | 16   | 1500      |

| MD18023CWAC | 12V  | YES | DIS    | SOW-16  | 16   | 1500      |

| MD18023ANAC | 5V   | YES | DIS    | SOP-16  | 16   | 3000      |

| MD18023BNAC | 8V   | YES | DIS    | SOP-16  | 16   | 3000      |

| MD18023CNAC | 12V  | YES | DIS    | SOP-16  | 16   | 3000      |

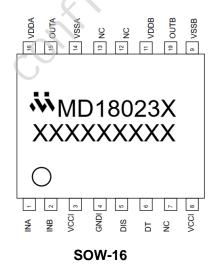

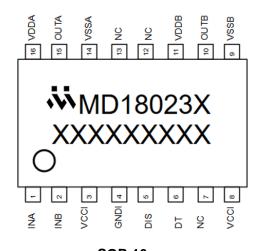

# 6. Package Reference and PIN Functions

(please refer to MRX-DM-SCM-04 for detailed rules)

SOP-16

| Na      | ame     |          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------|---------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SOW-16  | SOP-16  | Symbol   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1       | 1       | INA      | Input signal for channel A. Input of Channel A with internal pull-down resistance to GNDI.                                                                                                                                                                                                                                                                                                                                                     |

| 2       | 2       | INB      | Input signal for channel B. Input of Channel B with internal pull-down resistance to GNDI.                                                                                                                                                                                                                                                                                                                                                     |

| 3, 8    | 3, 8    | VCCI     | Primary-side (input side) supply voltage. Locally decoupled to GNDI using low ESR/ESL capacitor located as close to the device as possible.                                                                                                                                                                                                                                                                                                    |

| 4       | 4       | GNDI     | Primary-side (input side) ground reference. All signals in the primary side are referenced to this ground.                                                                                                                                                                                                                                                                                                                                     |

| 5       | 5       | DIS      | Disables both driver outputs if asserted high, enables if set low or left open. This pin is pulled low internally if left open. It is recommended to tie this pin to ground if not used to achieve better noise immunity. Bypass using 1nF low ESR/ESL capacitor close to DIS pin when connecting to a micro controller with distance.                                                                                                         |

| 6       | 6       | DT       | Programmable dead time function. Tying DT to VCCI allows the outputs to overlap. Placing a $5k\Omega$ to $200k\Omega$ resistor (R <sub>DT</sub> ) between DT and GNDI adjusts dead time according to: DT (ns) = 12 x R <sub>DT</sub> ( $k\Omega$ ). It is recommended to parallel a ceramic capacitor, 470 pF or lower, close to the DT pin with R <sub>DT</sub> to achieve better noise immunity. It is not recommended to leave DT floating. |

| 7,12,13 | 7,12,13 | NC       | No Internal connection.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 9       | 9       | VSSB (1) | Ground for secondary-side driver A. Ground reference for secondary side B channel.                                                                                                                                                                                                                                                                                                                                                             |

| 10      | 10      | OUTB     | Output of Channel B                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 11      | 11      | VDDB (1) | Secondary-side power for driver B. Locally decoupled to VSSB using a low ESR/ESL capacitor located as close to the device as possible.                                                                                                                                                                                                                                                                                                         |

| 14      | 14      | VSSA (1) | Ground for secondary-side driver A. Ground reference for secondary side A channel.                                                                                                                                                                                                                                                                                                                                                             |

| 15      | 15      | OUTA     | Output of Channel A                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 16      | 16      | VDDA (1) | Secondary-side power for driver A. Locally decoupled to VSSA using a low ESR/ESL capacitor located as close to the device as possible.                                                                                                                                                                                                                                                                                                         |

#### Note:

(1) VDD stands for VDDA or VDDB, VSS stands for VSSA or VSSB.

# 7. Specifications

## 7.1 Absolute Maximum Ratings

Over operating free air temperature range (unless otherwise noted) (1)

|                                                     | MIN  | MAX        | Unit              |

|-----------------------------------------------------|------|------------|-------------------|

| VCCI-GNDI                                           | -0.3 | 26         | V                 |

| INA, INB, DIS(EN)                                   | -10  | 26         | V.5               |

| DT                                                  | -0.3 | 26         | V                 |

| VDDA-VSSA, VDDB-VSSB                                | -0.3 | 30         | V                 |

| OUTA-VSSA, OUTB-VSSB                                | -0.3 | VDDA/B+0.3 | V                 |

| OUTA-VSSA, OUTB-VSSB, Transient for 200ns           | -2   | VDDA/B+0.3 | V                 |

| OUTA-VSSA, OUTB-VSSB, Transient for 100ns           | -5   | VDDA/B+0.3 | V                 |

| Junction Temperature (T <sub>J</sub> )              | -40  | 150        | °C                |

| Storage Temperature                                 | -65  | 150        | °C                |

| Channel A to Channel B Maximum Repetitive Isolation | (    | 1500       | V <sub>peak</sub> |

#### Note:

## 7.2 ESD Ratings

|                            |                                                                               | Value | Unit |

|----------------------------|-------------------------------------------------------------------------------|-------|------|

| Electrostatic              | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins (1)              | ±2000 | V    |

| discharge V <sub>ESD</sub> | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | ±1000 | V    |

#### Notes:

<sup>(1)</sup> Exceeding these ratings may cause permanent damage to the device. The device is not guaranteed to function outside of its operating conditions.

<sup>(1)</sup> ESD susceptibility, Human Body Model "HBM", according to AEC Q100-002.

<sup>(2)</sup> ESD susceptibility, Charged Device Model "CDM", according to AEC Q100-011.

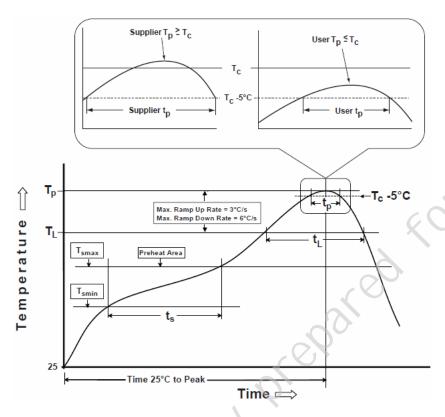

## 7.3 Recommended reflow profile

Figure 2. reflow curve

Table1. SnPb Eutectic Process-Classification Temperatures (Tc)

| Package Thickness | Volume mm₃<br><350 | Volume mm₃<br>≥350 |

|-------------------|--------------------|--------------------|

| <2.5 mm           | 235 ℃              | 220 °C             |

| ≥2.5 mm           | 220 °C             | 220 °C             |

Table2. Pb-Free Process-Classification Temperatures (Tc)

| Package Thickness | Volume mm³<br><350 | Volume mm³<br>350-2000 | Volume mm³<br>>2000 |

|-------------------|--------------------|------------------------|---------------------|

| <1.6 mm           | 260°C              | 260°C                  | 260°C               |

| 1.6 mm-2.5 mm     | 260°C              | 250°C                  | 245°C               |

| >2.5 mm           | 250°C              | 245°C                  | 245°C               |

**Table3. Classification Reflow Profiles**

| Profile Feature                                                                    | Sn-Pb Eutectic Assembly                                                                                                                                        | Pb-Free Assembly                                                                                                                                               |

|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preheat/Soak                                                                       |                                                                                                                                                                |                                                                                                                                                                |

| Temperature Min (T <sub>smin</sub> )                                               | 100 °C                                                                                                                                                         | 150 °C                                                                                                                                                         |

| Temperature Max (T <sub>smax</sub> )                                               | 150°C                                                                                                                                                          | 200 ℃                                                                                                                                                          |

| Time (t <sub>s</sub> ) from (T <sub>smin</sub> to T <sub>smax</sub> )              | 60-120 seconds                                                                                                                                                 | 60-120 seconds                                                                                                                                                 |

| Ramp-up rate (T∟to T <sub>P</sub> )                                                | 3°C/second max                                                                                                                                                 | 3°C/second max                                                                                                                                                 |

| Liquidous temperature (TL) Time                                                    | 183°C                                                                                                                                                          | 217℃                                                                                                                                                           |

| (t∟) maintained above T∟                                                           | 60-150 seconds                                                                                                                                                 | 60-150 seconds                                                                                                                                                 |

| Peak package body<br>temperature (T <sub>P</sub> )                                 | For users T <sub>P</sub> must not exceed the classification temp in Table1 For suppliers T <sub>P</sub> must equal or exceed the classification temp in Table1 | For users T <sub>P</sub> must not exceed the classification temp in Table2 For suppliers T <sub>P</sub> must equal or exceed the classification temp in Table2 |

| Time (t <sub>P</sub> ) within 5°C of the specified classification temperature (Tc) | 20 seconds                                                                                                                                                     | 30 seconds                                                                                                                                                     |

| Ramp-down rate (T⊦ to T∟)                                                          | 6°C/second max                                                                                                                                                 | 6°C/second max                                                                                                                                                 |

| Time 25°C to peak temperature                                                      | 6 minutes max                                                                                                                                                  | 8 minutes max                                                                                                                                                  |

<sup>\*</sup>Tolerance for peak profile temperature (TP) is defined as a supplier minimum and a user maximum

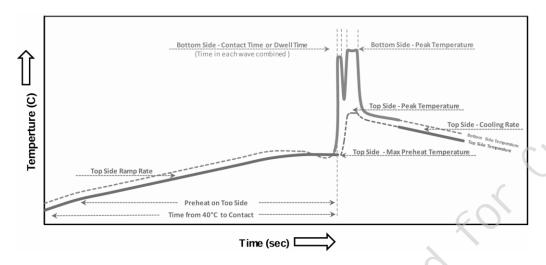

## 7.4 Recommended Wave Soldering Profile

Figure 3. Wave Soldering Curve

#### **Recommended Parameters for Solder Pot Temperature**

| Profile Feature  | General Profile IPC/JEDEC 1 |

|------------------|-----------------------------|

| Tin-Lead Alloys  | 230 – 260 °C                |

| Lead-Free Alloys | 260 – 290 °C                |

<sup>\*</sup>Temperatures can start as low as 240°C depending on the application and alloy being used.

#### **Recommended Parameters for VOC-Free**

| Profile Feature                  | General Profile  IPC/JEDEC1 | Tin-Lead Alloys (Recommended starting point) <sup>2</sup> | Lead-Free Alloys (Recommended starting point) <sup>3</sup> |

|----------------------------------|-----------------------------|-----------------------------------------------------------|------------------------------------------------------------|

| Top Side Ramp Up Rate            | < 3 °C/ Sec.                | 1 - 3 °C/ Sec.                                            | 1 - 3 °C/ Sec.                                             |

| Top Side Max Preheat Temperature | < 150 °C                    | 90 – 120 °C                                               | 90 – 140 °C                                                |

| Bottom Side Contact Time         | < 10 Sec.                   | < 5 Sec.                                                  | < 8 Sec.                                                   |

| Top Side Cooling Rate            | < 3 °C / Sec.               | < 3 °C / Sec.                                             | < 3 °C / Sec.                                              |

| Time from 40°C to Contact        | 60 – 240 Sec.               | 60 – 180 Sec.                                             | 60 – 180 Sec.                                              |

<sup>1</sup> The general profile data are the parameters allowable by IPC/JEDEC, and are added only as a reference.

<sup>2</sup> This data guideline applies to common tin-lead alloys (i.e. Sn63/Pb37, Sn62/Pb36/Ag2).

<sup>3</sup> This data guideline applies to common lead-free alloys (i.e. AIM REL Alloys, SAC, SN100C et.al.)

# 7.5 Recommended Hand Soldering and Desoldering Methods

#### **Hand Soldering**

| Selection of soldering iron | Flux                                                                                    | Iron temperature                                             | Welding time                                                                        |

|-----------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Sharp tip or cutting head   | Use rosin type or<br>non-cleaning flux<br>(with a small amount<br>of auxiliary wetting) | Sn Pb solder: 300-350°C<br>Lead free solder: 350-<br>400 ° C | 2-4 seconds per solder joint (to avoid overheating and damaging components or PCBs) |

#### Notes:

- (1) Heat the solder pad first, then send the solder wire.

- (2) Avoid forcefully pressing the soldering iron tip.

- (3) Pay attention to hand soldering ESD.

#### **Hand Desoldering**

| Selection of desoldering tool                   | Use solder suction cups and soldering irons                                                                                                         | Use hot air gun                                                                                                                                                                                                    |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Solder sucker and soldering iron or Hot air gun | Iron temperature: Sn Pb<br>solder: 300-350°C; Lead free<br>solder: 350-400 ° C;<br>Operation: Quickly heat the<br>solder joint and then tin suction | Temperature: 300-400°C Airflow: medium to low (to avoid blowing small components off). Time: ≤ 10 seconds/solder joint. Preheating plate: 150-180 ° C (bottom heating). Hot air nozzle: 250-300 ° C (top heating). |

#### Notes:

- (1) Clean the residual solder flux on the solder pads after desoldering.

- (2) Multilayer boards should be carefully avoided to prevent Pad detachment.

# 7.6 Recommended Operating Conditions

|                                    | MIN  | MAX | Unit |

|------------------------------------|------|-----|------|

| VCCI-GNDI                          | 3.0  | 24  | V    |

| INA, INB, DIS(EN)                  | -8   | 24  | V    |

| VDDA-VSSA, VDDB-VSSB for A Version | 5.5  | 28  | V    |

| VDDA-VSSA, VDDB-VSSB for B Version | 8.5  | 28  | V    |

| VDDA-VSSA, VDDB-VSSB for C Version | 12.5 | 28  | V    |

| Junction Temperature               | -40  | 140 | °C   |

| Ambient Temperature                | -40  | 125 | °C   |

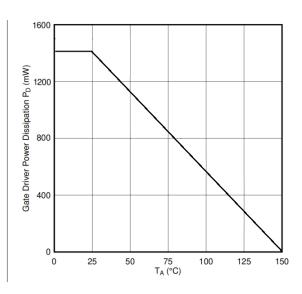

#### 7.7 Thermal Information (1)

|        | $R_{\theta JA}$ | R <sub>eJC</sub> | Unit |

|--------|-----------------|------------------|------|

| SOP-16 | 122.3           | 38.1             | °C/W |

| SOW-16 | 104.3           | 30.4             | °C/W |

#### Note:

(1) According to JEDEC JESD51-2, JESD51-7 at natural convection on FR4 1s0p board

Meraki confidential

# 7.8 Insulation Specifications

|                                           |                                                              |                                       | Val    | ue       |                   |

|-------------------------------------------|--------------------------------------------------------------|---------------------------------------|--------|----------|-------------------|

| Description                               | Test Condition                                               | Symbol                                | SOW-16 | SOP-16   | Unit              |

| Min. External Air Gap                     |                                                              | CLR                                   | 8      | 4        | mm                |

| (Clearance)                               |                                                              | CLR                                   | 0      | 4        | mm                |

| Min. External Tracking                    |                                                              | CPG                                   | 8      | 4        | mm                |

| (Creepage)                                |                                                              | CFG                                   | 0      | 4        | 111111            |

| Distance through the                      |                                                              | DTI                                   | 100    | 50       | um                |

| Insulation                                |                                                              | ווט                                   | 100    | 30       | um                |

| Comparative Tracking                      | DIN EN 60112                                                 | СТІ                                   | >60    | 00       | V                 |

| Index                                     | BIN EN OUT IZ                                                | 011                                   | 700    | 50       | V                 |

| Material Group                            | IEC 60112                                                    |                                       | I      | <u> </u> |                   |

| Insulation Specification                  | n per EN 60747-17                                            |                                       |        |          |                   |

| Climatic Category                         |                                                              |                                       | 40/12  | 5/21     |                   |

| Pollution Degree                          |                                                              |                                       | 2      |          |                   |

| Maximum Working                           | AC voltage                                                   | $V_{\text{IOWM}}$                     | 1250   | 700      | $V_{RMS}$         |

| Isolation Voltage                         | DC voltage                                                   | VIOWM                                 | 1768   | 990      | $V_{DC}$          |

| Maximum Repetitive                        |                                                              | VIORM                                 | 1768   | 990      | V .               |

| Isolation Voltage                         |                                                              | VIORM                                 | 1700   | 990      | V <sub>peak</sub> |

|                                           | $V_{\text{ini.b}} = V_{\text{IOTM}}$                         | <i>O</i> .                            |        |          |                   |

|                                           | $V_{pd(m)} = V_{IORM} \times 1.5$                            | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |        | 4050     | \ /               |

|                                           | $t_{ini} = t_m = 1 \text{ sec}$<br>$q_{pd} \le 5pC$          | $V_{pd(m)}$                           |        | 1050     | $V_{RMS}$         |

| Input to Output Test                      | 100% production test                                         |                                       |        |          |                   |

| Voltage, Method B1                        | V <sub>ini,b</sub> = V <sub>IOTM</sub>                       |                                       |        |          |                   |

| J ,                                       | $V_{pd(m)} = V_{IORM} \times 1.875$                          |                                       |        |          |                   |

|                                           | $t_{ini} = t_m = 1 \text{ sec}$                              | $V_{pd(m)}$                           | 2344   |          | $V_{RMS}$         |

|                                           | $q_{pd} \leq 5pC$                                            |                                       |        |          |                   |

|                                           | 100% production test  V <sub>ini.a</sub> = V <sub>IOTM</sub> |                                       |        |          |                   |

|                                           | $V_{\text{pd(m)}} = V_{\text{IORM}} \times 1.3$              |                                       |        |          |                   |

| Input to Output Test                      | $t_{\text{ini}} = 60 \text{ sec}$                            | $V_{pd(m)}$                           |        | 910      | $V_{RMS}$         |

| Voltage, Method A.                        | q <sub>pd</sub> ≤ 5pC                                        |                                       |        |          |                   |

| After Environmental                       | $V_{ini.a} = V_{IOTM}$                                       |                                       |        |          |                   |

| Tests Subgroup 1                          | $V_{pd(m)} = V_{IORM} \times 1.6$                            | $V_{pd(m)}$                           | 2000   |          | $V_{RMS}$         |

|                                           | $t_{ini} = 60 \text{ sec}$                                   | · pu(III)                             |        |          | TRINO             |

| Input to Output Toot                      | $q_{pd} \leq 5pC$                                            |                                       |        |          |                   |

| Input to Output Test                      | $V_{\text{ini.a}} = V_{\text{IOTM}}$                         |                                       |        |          |                   |

| Voltage, Method A. After Input and Output | $V_{pd(m)} = V_{IORM} \times 1.2$ $t_{ini} = 60 \text{ sec}$ | W                                     | 1500   | 840      | \/                |

| Safety Test Subgroup 2                    | $t_{ini} = 00 \text{ sec}$<br>$t_{m} = 10 \text{ sec}$       | $V_{pd(m)}$                           | 1500   | 040      | $V_{RMS}$         |

| 1 .                                       | $q_{pd} \leq 5pC$                                            |                                       |        |          |                   |

| and Subgroup 3  Maximum Transient         | " '                                                          |                                       |        |          |                   |

| Isolation Voltage                         | t = 60 sec                                                   | $V_{IOTM}$                            | 8000   | 4242     | $V_{peak}$        |

| isolation voltage                         | Test method per IEC62368-1,                                  | Vicari                                |        | 5000     | \/ .              |

|                                           | 1691 Helliou pel 16002308-1,                                 | V <sub>IOSM</sub>                     |        | 5000     | $V_{peak}$        |

| Maximovina Course                  | 1.2/50us waveform, V <sub>TEST</sub> = 1.3 x V <sub>IOSM</sub>                                   |                 |      |                 |            |

|------------------------------------|--------------------------------------------------------------------------------------------------|-----------------|------|-----------------|------------|

| Maximum Surge<br>Isolation Voltage | Test method per IEC62368-1,<br>1.2/50us waveform, V <sub>TEST</sub> =<br>1.6 x V <sub>IOSM</sub> |                 | 8000 |                 | $V_{peak}$ |

|                                    | $V_{IO} = 500 \text{ V}, T_{amb} = 25^{\circ}\text{C}$ > $10^{12}$                               |                 | 012  |                 |            |

| Isolation Resistance               | VIO = 500 V                                                                                      | R <sub>IO</sub> | > 1  | O <sup>11</sup> | Ωχ         |

| iodiation registarios              | 100°C ≤ Tamb ≤ 125°C                                                                             | TVIO            |      |                 | 1 1        |

|                                    | $V_{IO}$ = 500 V, $T_{amb}$ = $T_{S}$                                                            |                 | > 1  | 09              | 5          |

| Isolation Capacitance              | f = 1MHz                                                                                         | $C_{1O}$        | 1.   | 0               | pF         |

|                                    | UL 1577                                                                                          |                 |      |                 |            |

| Withstand Isolation                | $V_{TEST} = 1.2 \times V_{ISO,} t = 1 \text{ sec}$                                               | $V_{ISO}$       | 5700 | 3000            | $V_{RMS}$  |

| Voltage                            | 100% production test                                                                             | • 150           | 0.00 | 3300            | ♣ KINI2    |

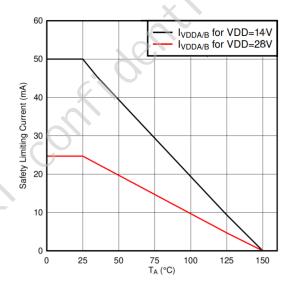

# 7.9 Safety-Limiting Values (1)

| Parameter                          | Symbol | Conditions | Min | Тур | Max  | Unit                   |

|------------------------------------|--------|------------|-----|-----|------|------------------------|

| Cofety system it assembly assembly |        | VDD=14V    |     |     | 50   | mA                     |

| Safety output supply current       | Is     | VDD=28V    |     |     | 25   | mA                     |

|                                    |        | INPUT      |     |     | 20   | mW                     |

| Cofety comply power                | Б      | DRIVER A   |     |     | 700  | mW                     |

| Safety supply power                | Ps     | DRIVER B   |     |     | 700  | mW                     |

|                                    |        | Total      |     |     | 1420 | mW                     |

| Safety temperature                 | Ts     |            |     |     | 150  | $^{\circ}\!\mathbb{C}$ |

#### Notes:

- (1) Safety limiting intends to minimize potential damage to the isolation barrier upon failure of input or output circuitry.

- (2) The maximum safety temperature ( $T_s$ ) has the same value as the maximum junction temperature ( $T_s$ ). The maximum limits of  $I_s$ and Ps should not be exceeded. These limits vary with the ambient temperature (TA).

## 7.10 Safety-Related Certifications

## The MD18023 (A/B/C) WAC (SOW16)

| Certified according to EN IEC 60747-17:2020+AC                                                                                                                                                              | UL 1577 Component<br>Recognition Program                     | certification per GB4943.1-<br>2022 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------|

| Reinforced insulation  Maximum transient isolation voltage, 8000 V <sub>PK</sub> .  Maximum repetitive peak isolation voltage, 1768 V <sub>PK</sub> ; Maximum surge isolation voltage, 8000 V <sub>PK</sub> | Single Protection,<br>5700V <sub>RMS</sub> Isolation Voltage | Reinforced insulation               |

| R 50671084                                                                                                                                                                                                  | E537168                                                      | CQC25001465308                      |

#### The MD18023 (A/B/C) NAC (SOP16)

| Certified according to EN IEC 60747-17:2020+AC                                                                                                                                                        | UL 1577 Component<br>Recognition Program                  | certification per GB4943.1-<br>2022 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------------|

| Basic insulation  Maximum transient isolation voltage, 4242 V <sub>PK</sub> .  Maximum repetitive peak isolation voltage, 990 V <sub>PK</sub> ; Maximum surge isolation voltage, 5000 V <sub>PK</sub> | Single Protection, 3000V <sub>RMS</sub> Isolation Voltage | Basic insulation                    |

| R 50671084                                                                                                                                                                                            | E537168                                                   | CQC25001465300                      |

#### 7.11 Electrical Characteristics

VCCI = 3.3 V or 5 V,  $0.1\mu F$  capacitor from VCCI to GNDI,  $V_{VDD}$ = 15 V,  $1\mu F$  capacitor from VDD to VSS, DT pin tied to VCCI,  $C_L = 0$  PF, TA = -40°C to +125°C, (unless otherwise noted)

| Parameter                             | Symbol                          | Conditions                                  | Min  | Тур      | Max  | Unit |

|---------------------------------------|---------------------------------|---------------------------------------------|------|----------|------|------|

| Supply Currents                       |                                 |                                             |      |          | •    |      |

| VCCI quiescent current                | lvcci_off                       | INA = INB = 0V<br>VCCI=5V                   | 0.7  | 1.3      | 2.4  | mA   |

| VDDA(B) quiescent current             | I <sub>VDDA(B)_</sub> OFF       | INA = INB = 0V<br>VDD=15V                   | 0.7  | 1.2      | 1.8  | mA   |

| VCCI operating current                | I <sub>VCCI_ON</sub>            | f <sub>INA</sub> =f <sub>INB</sub> = 500kHz |      | 5.0      | 9.0  | mA   |

| VDDA(B) operating current             | I <sub>VDDA(B)</sub> ON         | Duty = 50%<br>C <sub>LOAD</sub> =100pF      |      | 3.0      | 5.0  | mA   |

| Inputs (INA, INB, DIS)                |                                 |                                             |      | <b>)</b> |      |      |

| Input voltage rising threshold        | V <sub>ITH</sub>                | 4                                           | 1.55 | 1.75     | 1.95 | V    |

| Input voltage falling threshold       | $V_{ITL}$                       | 9                                           | 0.6  | 0.75     | 0.95 | V    |

| Input voltage hysteresis              | $V_{ITHYS}$                     | 300                                         |      | 1        |      | V    |

| Undervoltage Lockout                  |                                 |                                             |      |          |      |      |

| VCCI rising threshold                 | V <sub>CCIR</sub>               |                                             | 2.5  | 2.65     | 2.8  | V    |

| VCCI falling threshold                | $V_{CCIF}$                      | . 8                                         | 2.4  | 2.53     | 2.66 | V    |

| VCCI threshold hysteresis             | V <sub>CCIHYS</sub>             |                                             |      | 0.12     |      | V    |

| VDDA(B) rising threshold              | V <sub>DDA(B)R</sub>            |                                             | 5.2  | 5.5      | 5.8  | V    |

| VDDA(B) falling threshold             | V <sub>DDA(B)</sub> F           | For A Version                               | 4.9  | 5.2      | 5.5  | V    |

| VDDA(B) threshold hysteresis          | V <sub>DDA(B)HYS</sub>          |                                             | 0.1  | 0.3      | 0.5  | V    |

| VDDA(B) rising threshold              | V <sub>DDA(B)R</sub>            |                                             | 7.7  | 8.3      | 8.9  | V    |

| VDDA(B) falling threshold             | V <sub>DDA(B)F</sub>            | For B Version                               | 7    | 7.6      | 8.2  | V    |

| VDDA(B) threshold hysteresis          | V <sub>DDA(B)HYS</sub>          |                                             | 0.4  | 0.7      | 1    | V    |

| VDDA(B) rising threshold              | V <sub>DDA(B)R</sub>            |                                             | 10.5 | 12       | 13.5 | V    |

| VDDA(B) falling threshold             | $V_{DDA(B)F}$                   | For C Version                               | 9.5  | 10.5     | 11.5 | V    |

| VDDA(B) threshold hysteresis          | V <sub>DDA(B)HYS</sub>          |                                             | 1    | 1.5      | 2    | V    |

| OUTPUTS (OUTA, OUTB)                  |                                 | I                                           |      |          | 1    | I    |

| Source peak current                   | I <sub>SRC</sub> <sup>(1)</sup> | $C_{LOAD} = 0.22uF$<br>$F_{SW} = 1kHz$      |      | 4        |      | А    |

| Sink peak current                     | I <sub>SNK</sub> <sup>(1)</sup> |                                             |      | 7        |      | Α    |

| High output voltage                   | V <sub>OH</sub>                 | $I_{OUT} = -10mA$                           |      | 12       | 20   | mV   |

| Low output voltage                    | V <sub>OL</sub>                 | I <sub>OUT</sub> = 10mA                     |      | 6        | 10   | mV   |

| Output pullup resistance              | RoH                             | I <sub>OUT</sub> = -10mA                    |      | 1.2      | 2    | Ω    |

| Output pulldown resistance            | R <sub>OL</sub>                 | I <sub>OUT</sub> = 10mA                     |      | 0.6      | 1    | Ω    |

| DEAD TIME AND OPERLAP PR              |                                 | •                                           | •    |          |      |      |

|                                       |                                 | DT tied to VCCI                             |      | Ove      | rlap |      |

| Dead time                             | D-                              | Open                                        | 5    |          |      | us   |

| DT (ns) = 12 x $R_{DT}$ (k $\Omega$ ) | DT                              | $R_{DT} = 5k\Omega$                         | 50   | 70       | 90   | ns   |

| • •                                   |                                 | $R_{DT} = 20k\Omega^{(1)}$                  | 200  | 240      | 280  | ns   |

| Rise time                                 |                          |                                                      | 12  | 16 | r |

|-------------------------------------------|--------------------------|------------------------------------------------------|-----|----|---|

| Fall time                                 | t <sub>R</sub>           | C <sub>LOAD</sub> =1.8nF<br>C <sub>LOAD</sub> =1.8nF | 8   | 12 | r |

| Minimum input pulse width                 |                          | CLOAD 1.GIA                                          | 50  | 80 |   |

| that passes to output                     | $t_{PWMIN}$              |                                                      |     |    | 1 |

| Rising propagation delay                  | t <sub>RPDA(B)</sub>     |                                                      | 70  | 90 | ı |

| Falling propagation delay                 | t <sub>FPDA(B)</sub>     |                                                      | 55  | 75 |   |

| Pulse width distortion                    | t <sub>PWD</sub>         | t <sub>RPDA(B)</sub> - t <sub>FPDA(B)</sub>          |     | 30 | ı |

| Channel A to Channel B delay              |                          | t <sub>RPDA</sub> - t <sub>RPDB</sub>                |     | 10 |   |

| match                                     | t <sub>PDM</sub>         | t <sub>fpda</sub> - t <sub>fpdb</sub>                |     | C  |   |

| VCCI power-up time delay                  | t <sub>start_</sub> vccı | INA = INB = High                                     | 55  | 90 |   |

| VDD power-up time delay                   | t <sub>start_VDD</sub>   | INA = INB = High                                     | 6   | 10 |   |

| Common Mode Transient<br>Immunity         | CMTI (1)                 |                                                      | 200 |    | \ |

| Note:                                     |                          |                                                      |     |    |   |

|                                           |                          | 1 blebak                                             | 2   |    |   |

| Not subject to production test, guarantee | by design.               |                                                      |     |    |   |

|                                           |                          | ~00                                                  |     |    |   |

|                                           |                          |                                                      |     |    |   |

|                                           |                          |                                                      |     |    |   |

|                                           |                          | ·O'                                                  |     |    |   |

|                                           |                          |                                                      |     |    |   |

|                                           |                          |                                                      |     |    |   |

|                                           |                          |                                                      |     |    |   |

|                                           |                          |                                                      |     |    |   |

|                                           |                          |                                                      |     |    |   |

|                                           | O                        |                                                      |     |    |   |

|                                           | i or                     |                                                      |     |    |   |

|                                           | 00                       |                                                      |     |    |   |

| •.                                        | 3) 05                    |                                                      |     |    |   |

|                                           | 9) 01                    |                                                      |     |    |   |

|                                           | 9) 00                    |                                                      |     |    |   |

|                                           | 9/06                     |                                                      |     |    |   |

|                                           | 9) 00                    |                                                      |     |    |   |

| den'i                                     | 3) 0                     |                                                      |     |    |   |

| E, 96UT                                   | 9/ 0/                    |                                                      |     |    |   |

| Si denti                                  | 9)                       |                                                      |     |    |   |

| - ONFI DENTI                              | 3)                       |                                                      |     |    |   |

| COULING                                   | 9/ 0/                    |                                                      |     |    |   |

|                                           |                          |                                                      |     |    |   |

|                                           | 3)                       |                                                      |     |    |   |

|                                           |                          |                                                      |     |    |   |

|                                           |                          |                                                      |     |    |   |

|                                           |                          |                                                      |     |    |   |

|                                           |                          |                                                      |     |    |   |

|                                           |                          |                                                      |     |    |   |

| Confidenti                                |                          |                                                      |     |    |   |

|                                           |                          |                                                      |     |    |   |

|                                           |                          |                                                      |     |    |   |

|                                           |                          |                                                      |     |    |   |

|                                           |                          |                                                      |     |    |   |

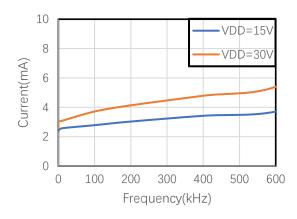

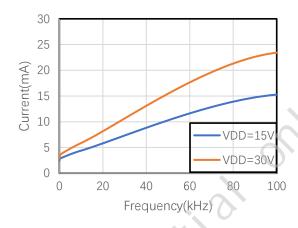

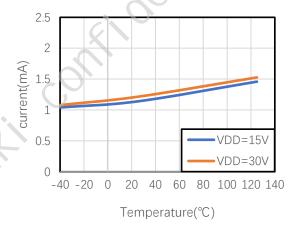

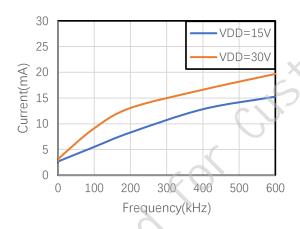

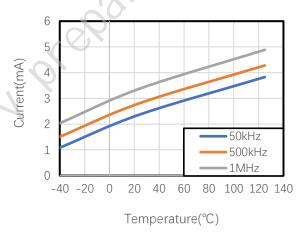

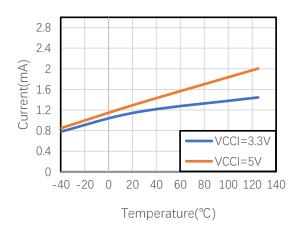

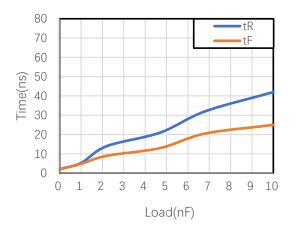

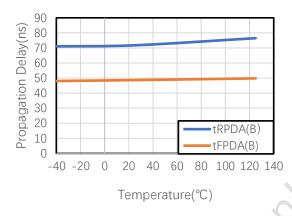

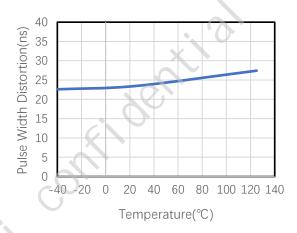

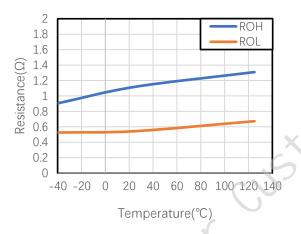

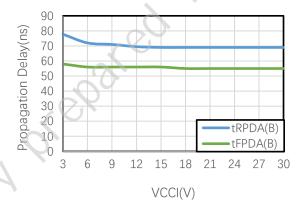

## 7.12 Typical Characteristics

VDD = 15V, VCCI = 3.3 V, T<sub>A</sub> = 25°C, no load unless otherwise noted.

Figure 4. Per Channel (IVDDA/B) Current Consumption Vs. Frequency (No Load)

Figure 6. Per Channel (I<sub>VDDA/B</sub>) Current Consumption Vs. Frequency (10nF Load)

Figure 8. Per Channel (IVDDA/B) Quiescent Supply Current vs Temperature (No Load, Input Low, No Switching)

Figure 5. Per Channel (IVDDA/B) Current Consumption Vs. Frequency (1nF Load)

Figure 7. Per Channel (IVDDA/B) Supply Current Vs.

Temperature (100-pF Load)

Figure 9. I<sub>VCCI</sub> Quiescent Supply Current vs Temperature (No Load, Input Low, No Switching)

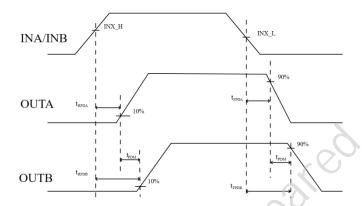

Figure 10. Rising and Falling Times

Figure 12. Propagation Delay

Figure 14. Pulse Width Distortion

Figure 11. Output Resistance

Figure 13. Propagation Delay

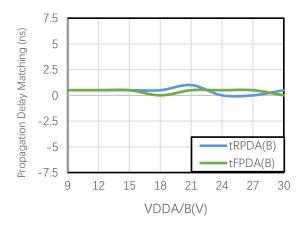

Figure 15. Propagation Delay Matching (tpdm)

Figure 16. Propagation Delay Matching (tpdm)

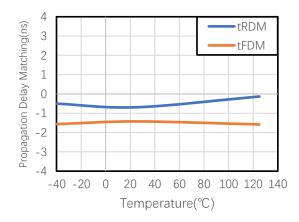

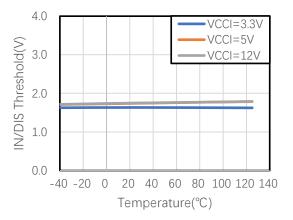

Figure 18. VDD UVLO Hysteresis

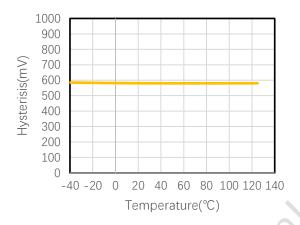

Figure 20. IN/DIS Fall Threshold

Figure 17. VDD UVLO Threshold

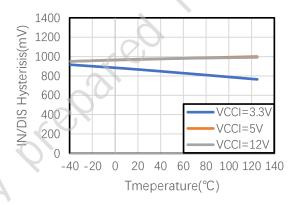

Figure 19. IN/DIS Hysteresis

Figure 21. IN/DIS Rise Threshold

## 8. Parameter Measurement Information

## 8.1 Propagation Delay and Pulse Width Distortion

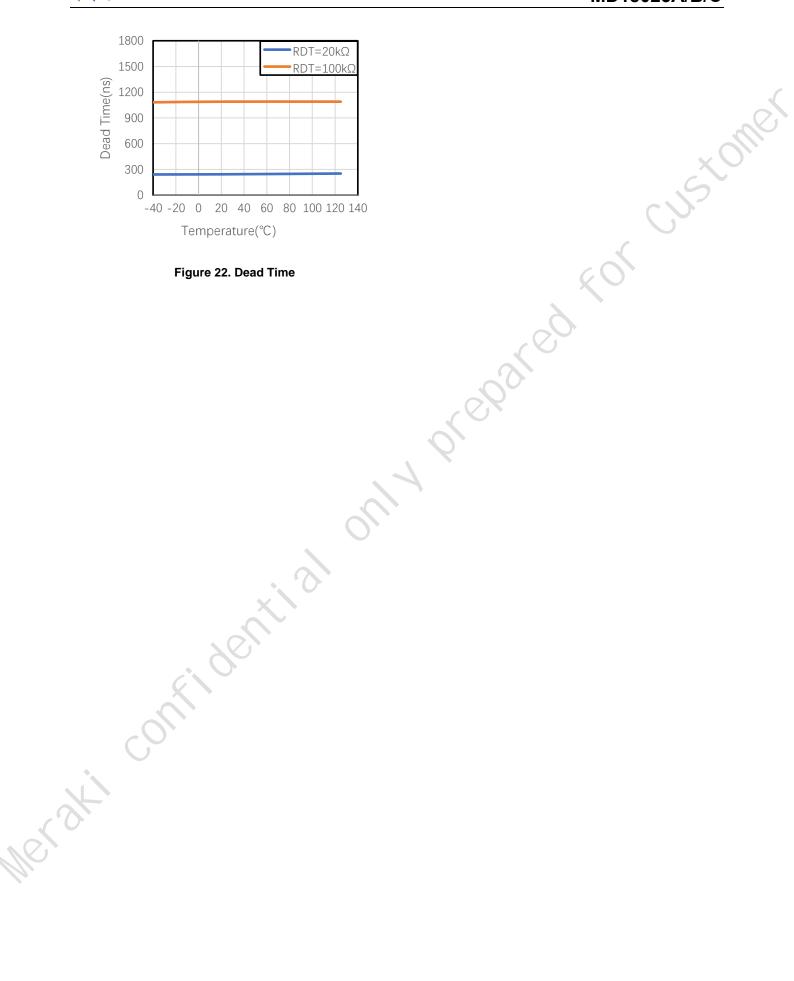

Figure 23 shows how one calculates pulse width distortion ( $t_{PWD}$ ) and delay matching ( $t_{PDM}$ ) from the propagation delays of channel A and channel B. It can be measured by ensuring that both inputs are in phase, and the dead time function disabled by shorting the DT Pin to VCCI.

Figure 23. Propagation Delay and Channel to Channel Delay Match Time, connect DT to VCCI

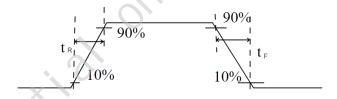

#### 8.2 Rising and Falling Time

Figure 24 shows the criteria for measuring rising (t<sub>R</sub>) and falling (t<sub>F</sub>) times.

Figure 24. Rising and Falling Time Criteria

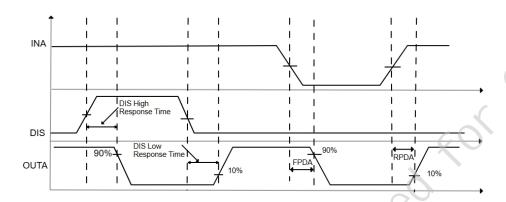

#### 8.3 Input and Disable Response Time

Figure 25 shows the response time of the disabled function. It is recommended to use a 1nF low ESR/ESL bypass capacitor close to DIS pin when connecting DIS pin to a micro controller with distance. For more information, see Disable Pin.

Figure 25. Disable Pin Timing

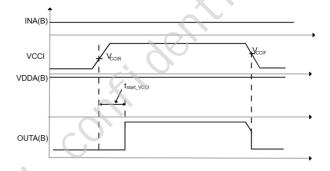

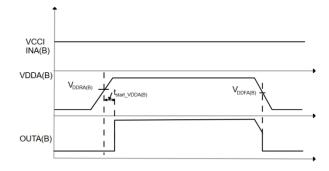

#### 8.4 Power-up UVLO Delay to Output

Before the driver is ready to deliver an appropriate output state, there is a power-up delay time from the rising edge of the undervoltage lockout (UVLO) to outputs, which is defined as t<sub>start VCCI</sub> to OUTA(B) for VCCI UVLO (typically 55us) and t<sub>start VDD</sub> to OUTA(B) for VDD UVLO (typically 6us). It is recommended to consider proper margin time before launching PWM signal after the driver's VCCI and VDD bias supply is ready. Figure 26 and Figure 27 show the power up UVLO delay timing diagram for VCCI and VDD.

If INA or INB are active before VCCI or VDD have crossed their respective turn-on thresholds, the output will not update until VCCI or VDD has exceeded its UVLO rising threshold by the t<sub>start\_VCCI</sub> to OUTA(B) or t<sub>start VDD</sub> to OUTA(B) duration.

Figure 27. VDD Power-up UVLO Delay

#### 8.5 CMTI Testing

Figure 28. Simplified CMTI Testing Setup

Meraki denti di

# 9. Detailed Descriptions

#### 9.1 Overview

The MD18023A/B/C is an isolated dual channel gate driver family designed with 4-A source current and 7-A sink current to drive IGBTs, Si and SiC MOSFETs. The device can be configured as two low-side drivers, two high-side drivers and a half bridge driver. The input side (primary-side) is isolated from the output side (secondary-side) by 5.7kV<sub>RMS</sub> isolation barrier with a minimum of 200 V/ns common mode transient immunity. The inputs can handle -10V to 26V DC voltage range, which increases robustness against ringing from parasitic inductance of long routing traces. Other features include resistor programmable dead time (DT PIN) control, disable(enable) feature to shutdown both outputs, and UVLO functions for all supplies.

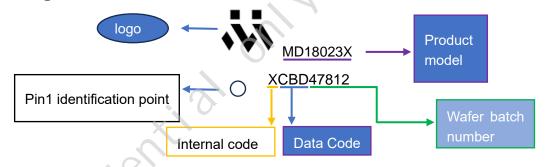

MD182023XNAC: The net weight of a single capsule is 166mg. MD18211XWAC: The net weight of a single capsule is 459.5mg.

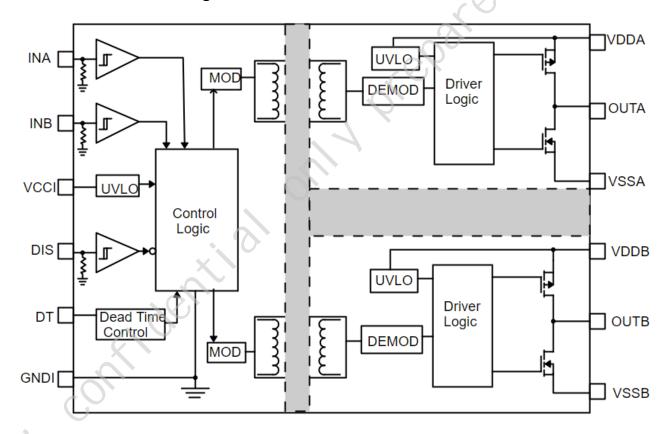

#### 9.2 Functional Block Diagram

#### 9.3 Input and Output Logic Table

MD18023A/B/C operates in normal mode and UVLO mode. In the normal mode, the output state is dependent on states of the input pins. See as below:

| Inp      | uts      | DIC | Out  | tputs | Note                                             |

|----------|----------|-----|------|-------|--------------------------------------------------|

| INA      | INB      | DIS | OUTA | OUTB  | Note                                             |

| L        | L        | Ш   | L    | L     | X                                                |

| L        | Н        | ┙   | L    | Η     | 5                                                |

| Н        | L        | L   | Н    | L     |                                                  |

| Н        | Н        | Ш   | L    | L     | DT is programmed with R <sub>DT</sub> & floating |

| Н        | Н        | ┙   | Н    | Η     | DT is pulled high to VCCI                        |

| Floating | Floating | Ш   | L    | L     | 60                                               |

|          |          |     |      |       | Bypass using 1-nF capacitor close to             |

| Any      | Any      | Н   | L    | L     | DIS (EN) pin when connecting to a micro-         |

|          |          |     |      |       | controller with distance.                        |

#### 9.4 Input Stage

The input pins of MD18023A/B/C are based on a TTL compatible input-threshold logic. The input voltage range is independent of the VCCI supply voltage. Since it has a typical high threshold ( $V_{\rm ITH}$ ) of 1.75V and a typical low threshold ( $V_{\rm ITL}$ ) of 0.75V, with little variation with temperature (Figure 20, Figure 21), and a wide hysteresis ( $V_{\rm ITHYS}$ ) of 1V for good noise immunity and stable operation, MD18023A/B/C is conveniently driven by PWM control signals derived from 3.3V and 5V digital power-controller devices. Although the internal pull-down resistors force the input port to pull it low while remaining open (See Functional Block Diagram), it is recommended to tie the input pins to the ground if it is not being used. Furthermore, Since the input side of the MD18023A/B/C is isolated from the output driver, and the input control is independent of VCCI, the input signal amplitude can be greater or less than VCCI as long as the recommended operating limits are not exceeded. When integrated with a control source in the system, greater flexibility can be maintained and users can select the most efficient VDD for the gate overdrive voltage of their choice.

## 9.5 Output Stage

The output stage of MD18023A/B/C features the PMOS as pull up structure and the pull-down structure with NMOS. PMOS provides the pull up capability when Input is 'HIGH'. and the R<sub>OH</sub> parameter is a DC measurement which is representative of the on-resistance of the P-Channel device. N-MOS provides the pull-down capability when Input is 'LOW', the R<sub>OL</sub> parameter is a DC measurement which is representative of the on-resistance of the N-Channel device. Both outputs of the MD18023A/B/C can deliver 4-A peak source and 7-A peak sink current pulses. The output voltage swings between VDD and VSS provides rail-to-rail operations due to the MOS-output stage which achieves very low drop-out. Additionally, the output channel A of the MD18023A/B/C is also isolated from output channel B. The output of one channel is effectively protected from interference from the other.

#### 9.6 Programmable Dead Time (DT) Pin

MD18023A/B/C allows the outputs to overlap by connecting this pin directly to VCCI. It is recommended to connect this pin to VCCI which disables dead time feature and achieves better nois e immunity.

When the DT pin is floating, a large dead time is designed to improve safety and reliability of the system, so as to prevent the dead time from failing due to resistance cold soldering and other reasons. This helps to quickly eliminate the risk of system failure due to too small dead time.

The dead time  $t_{DT}$  can be programmed by placing a resistor ( $R_{DT}$ ) between the DT pin and GNDI. It recommends bypassing this pin with a ceramic capacitor (470 pF or lower) close to DT pin to achieve better noise immunity and better dead time matching between both channels. The appropriate  $R_{DT}$  value can be determined from:

$$t_{DT}$$

(ns) $\approx$ 12×R<sub>DT</sub> (k $\Omega$ )

This feature increases the reliability of system, and the recommended value of  $R_{DT}$  is between  $5k\Omega$  and  $200k\Omega$ . When DT pin is shorted to GNDI, MD18023A/B/C locks the outputs of both channels with minimum dead time of 40ns.

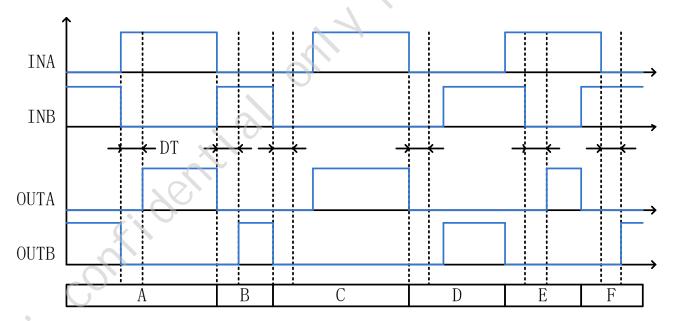

The programmed deadtime is activated by the input signal's falling edge to prevent shoot-through when the device is designed in an application of high side and low side driver. Various dead time logic operating conditions are illustrated and explained as below.

|   | Condition                     | Result                                                                        |

|---|-------------------------------|-------------------------------------------------------------------------------|

|   |                               | INB sets OUTB low immediately and allocates the programmed dead time to       |

| Α | INB goes low, INA goes high   | OUTA. OUTA is permitted to go high after the programmed dead time has         |

|   |                               | ended.                                                                        |

|   |                               | INA sets OUTA low immediately and allocates the programmed dead time to       |

| В | INB goes high, INA goes low   | OUTB. OUTB is permitted to go high after the programmed dead time has         |

|   |                               | ended.                                                                        |

|   |                               | INB sets OUTB low immediately and allocates the programmed dead time for      |

| С | INB goes low, INA remains low | OUTA. In this case, the inherent dead time of input signal is longer than the |

| O | IND goes low, INATERNALIS low | programmed dead time. Therefore, when INA goes high, it immediately sets      |

|   |                               | OUTA high.                                                                    |

|   |                               | INA sets OUTA low immediately and allocates the programmed dead time to       |

| _ | INA good low IND remains low  | OUTB. In this case, the input signal dead time is longer than the programmed  |

| D | INA goes low, INB remains low | dead time. When INB goes high after the duration of the input signal dead tin |

|   |                               | it immediately sets OUTB high.                                                |

|   |                               | To avoid overshoot, OUTB is immediately pulled low by the INA and remains     |

| _ | INA goes high, INB and OUTB   | OUTA low. After some time INB goes low and allocates the programmed dea       |

| Ε | keep high                     | time to OUTA. OUTB is already low. After the programmed dead time, OUTA       |

|   |                               | goes high.                                                                    |

|   |                               | To avoid overshoot, OUTA is immediately pulled low by INA and keeps OUTE      |

| _ | INB goes high, INA and OUTA   | low. After some time, INA goes low and allocates the programmed dead time     |

| F | keep high                     | OUTB. OUTA is already low. After the programmed dead time, OUTB goes          |

|   | , -                           | high.                                                                         |

|   | Confidenti                    |                                                                               |

# 10. Application and Implementation

#### 10.1 Application Information

The MD18023A/B/C effectively combines both isolation and buffer-drive functions. The flexible, universal capability of the MD18023A/B/C (with up to 24-V VCCI and 28-V VDDA/VDDB) allows the device to be used as a low-side, high-side, high-side/low-side or half-bridge driver for IGBTs or Si/SiC MOSFETs. With integrated components, advanced protection features (UVLO, dead time, and disable) and optimized switching performance; the MD18023A/B/C enable designers to build smaller, more robust designs for enterprise, telecom, automotive, and industrial applications with a faster time to market.

## **10.2 Typical Application**

Figure 29 shows an example which uses two supplies (or single-input-double-output power supply). Power supply  $V_1$  determines the positive drive output voltage and  $V_2$  determines the negative turn-off voltage. The configuration for channel B is the same as channel A. This solution requires more power supplies. However, it provides more flexibility when setting the positive and negative voltage rails.

Figure 29. Application Circuit

## 11. Layout

#### 11.1 Layout Guidelines

Designers must pay close attention to PCB layout to achieve optimum performance for the MD18023A/B/C. Some key guidelines are:

#### Component placement:

- Low-ESR and low-ESL capacitors must be connected close to the device between the VCCI and GNDI pins and between VDD and VSS pins to suppress switching spikes and to support high peak currents when turning on the external power devices.

- To avoid larger negative transient spikes on the VSS pins connected to the switch node, the parasitic inductances between the source of the top power device and the source of the bottom power device must be minimized.

- It is recommended to place the dead-time setting resistor, R<sub>DT</sub>, and its bypassing capacitor close to DT pin of the MD18023A/B/C.

- It is recommended to bypass using a 1nF low ESR/ESL capacitor,  $C_{\text{DIS}}$ , close to DIS pin when connecting to a micro controller with distance.

#### Grounding considerations:

– Limiting the high peak currents that charge and discharge the gates of the power devices to a minimal physical area is essential. This limitation decreases the loop inductance and minimizes noise on the gate terminals of the power devices. The gate driver must be placed as close as possible to the power devices.

#### High-voltage considerations:

– To ensure isolation performance between the primary and secondary side, avoid placing any PCB traces or copper below the driver device. A PCB cutout or groove is recommended to prevent contamination that may compromise the isolation performance.

#### Thermal considerations:

- -Increasing the PCB copper connection to the VDD and VSS pins is recommended, with priority on maximizing the connection to VSS. However, the previously mentioned high-voltage PCB considerations must be maintained.

- -If the system has multiple layers, we also recommend connecting the VDD and VSS pins to internal ground or power planes through multiple vias of adequate size. These vias should be located close to the IC pins to maximize thermal conductivity. However, keep in mind that no overlapping between traces or coppers from different high voltage planes.

## 11.2 Layout Example

Figure 30. Layout Example

Meraki confidential onli

# 12. Mechanical Data and Land Pattern Data

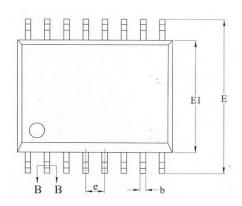

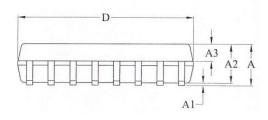

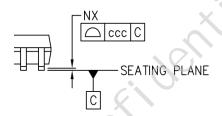

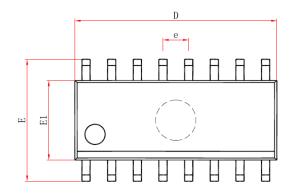

# 12.1 SOW16(300mil)

Figure 31. Top View

Figure 33. Side View

Figure 34. Coplanarity View

Figure 32. Side View

| Symbol | Dimensions      | In Millimeters |  |  |  |

|--------|-----------------|----------------|--|--|--|

|        | MIN             | MAX            |  |  |  |

| А      | ı               | 2.65           |  |  |  |

| A1     | 0.10            | 0.30           |  |  |  |

| A2     | 2.25            | 2.35           |  |  |  |

| b      | 0.35            | 0.43           |  |  |  |

| С      | 0.25            | 0.29           |  |  |  |

| D      | 10.20           | 10.40          |  |  |  |

| E      | 10.10           | 10.50          |  |  |  |

| E1     | 7.40            | 7.60           |  |  |  |

| е      | 1.27(BSC)       |                |  |  |  |

| L      | 0.55            | 0.85           |  |  |  |

| θ      | 0°              | 8°             |  |  |  |

| Copla  | narity(ccc) ≤ 0 | ).10mm         |  |  |  |

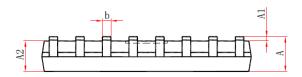

# 12.2 SOP16(150mil)

Figure 35. Top View

Figure 36. Side View

Figure 37. Side View

Figure 38. Coplanarity View

| Clymbal | Dimensions      | s In Millimeters |

|---------|-----------------|------------------|

| Symbol  | MIN             | MAX              |

| А       | -               | 1.75             |

| A1      | 0.10            | 025              |

| A2      | 1.30            | 1.50             |

| b       | 0.33            | 0.51             |

| С       | 0.17            | 0.25             |

| D       | 9.80            | 10.20            |

| E       | 5.80            | 6.20             |

| E1      | 3.80            | 4.00             |

| е       | 1.27            | 7(BSC)           |

| L       | 0.4             | 1.27             |

| θ       | 0°              | 8°               |

| Copla   | narity(ccc) ≤ 0 | ).10mm           |

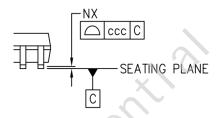

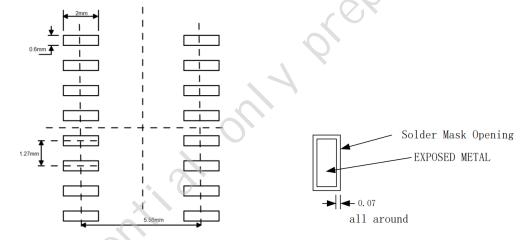

#### 12.3 Land Pattern Data

Figure 39. SOW-16 Land Pattern Data

Figure 40. SOP-16 Land Pattern Data

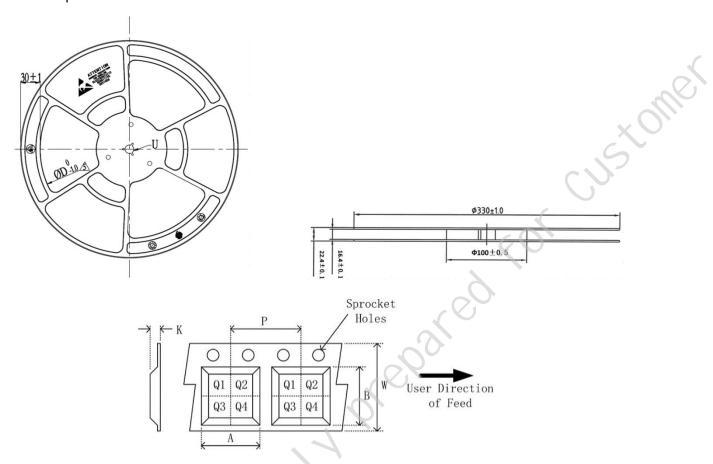

#### Reel and Tape Information

Figure 41. Reel Dimensions

| Devise          | Package<br>Type | Pins | SPQ<br>(pcs) | A(mm)             | B(mm)     | K(mm)   | P(mm)   | W(mm)  | Pin1<br>Quadrant |

|-----------------|-----------------|------|--------------|-------------------|-----------|---------|---------|--------|------------------|

| MD18023A/B/CNAC | SOP16           | 16   | 3000         | 6.7±0.1           | 10.4 ±0.1 | 2.1±0.1 | 8±0.1   | 16±0.3 | Q1               |

| MD18023A/B/CWAC | SOW16           | 16   | 1500         | 10.9 <u>±</u> 0.1 | 10.8 ±0.1 | 3.0±0.1 | 12 ±0.1 | 16±0.3 | Q1               |

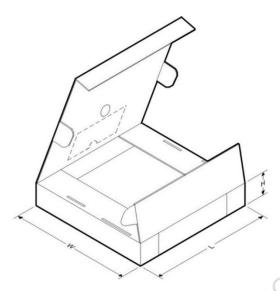

# 13. Tape and Reel Box Dimensions

Figure 42. Box Dimensions

PART NO.: MD18023CWAC

RANGE:

PACKAGE: SOP16

QUANTITY: 1500PCS

DATE CODE: XXXXXXXXX

LOT NO.: XXXXXXX

DATE: XXXX/XX/XX

C02/W02,W03 WF: AT: C02/A04

(Please refer to MRX-DM-QA-05 for detailed rules)

| Device          | Package Type | Pins | SPQ (pcs) | Length(mm) | Width(mm) | Height(mm) |

|-----------------|--------------|------|-----------|------------|-----------|------------|

| MD18023A/B/CNAC | SOP16        | 16   | 6000      | 360        | 360       | 65         |

| MD18023A/B/CWAC | SOW16        | 16   | 3000      | 360        | 360       | 65         |